リコンフィギャラブルシステム

-

リコンフィギャラブルシステムとは、その名の通りアーキテクチャの構成が柔軟に変更可能なシステムのことです。

例えば、従来の使用用途が限定されたチップ(ASIC)と異なり、使用用途によって適した構成をチップの製造後に決定することができます。

ASICはその特定の用途によっては消費電力などの効率が良いのですが、システムの仕様変更などは容易ではありません。

最近では、最新のプロセス技術などを取り込むことによりこの消費電力の効率の問題も徐々に解消され始め、産業界等で幅広く使われています。

ふんが研では、リコンフィギャラブルアーキテクチャを持つチップを実際に作成し、様々な学会や論文誌へ発表しています。

Cool Mega Array (超低電力アクセラレータ)

-

Cool Mega Arrayとはふんが研で開発されたリコンフィギャラブルなアクセラレータで沢山の演算器を持つPE-ARRAYと、

それを制御するマイクロコントローラから成ります。

このアクセラレータはアプリケーションが決まった段階で、構成情報をデータとして取得して、その情報に基づいてロジックの構成が変化するアクセラレータです。

最大の特徴は、演算器と演算器の間に一切のレジスタがなく一度データを放り投げてしばらくすると正しいデータが取得できる点にあります。

これにより、レジスタに必要なクロックの分配や電力などを削減することができ、高い電力効率を達成することができます。

過去には電力効率世界一を達成した、ふんが研一押しの研究です。

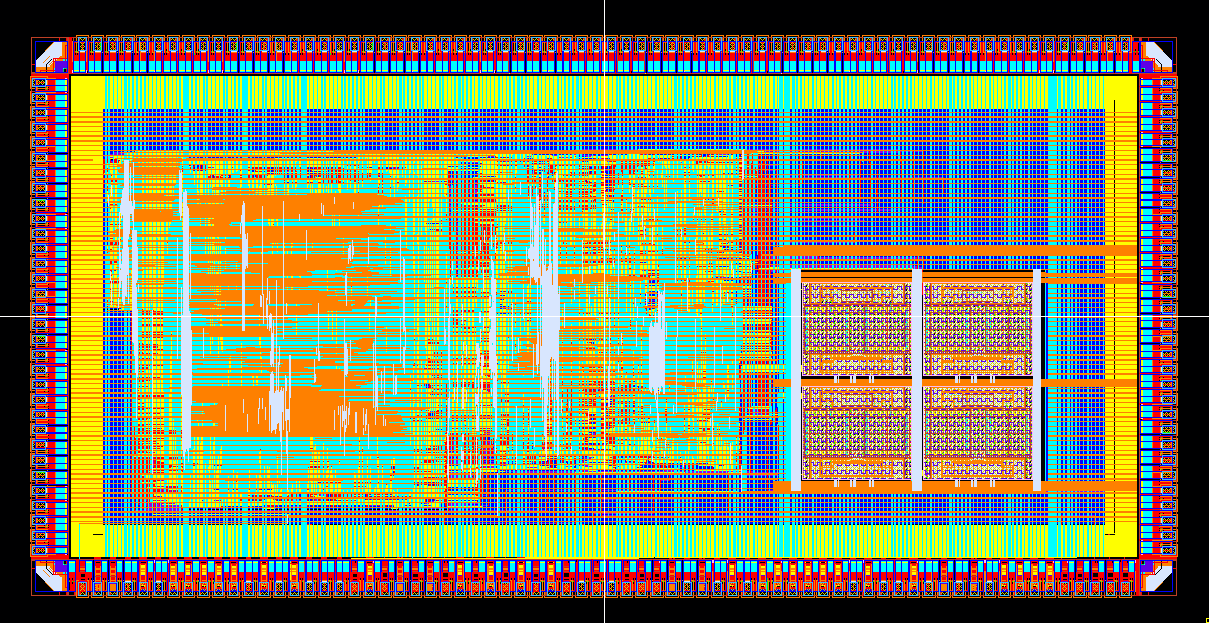

CMAのレイアウト図 SOTB65nm FD-SOIプロセス使用

Cube (インダクタを用いた無線によるチップ間通信チップ)

-

これはビルディングブロック型コンピューティングシステムという,

チップをあたかもレゴブロックのように組み替えることができるシステムを

作ろうという研究のひとつです。

Cubeは、電子学科の黒田研究室の開発した、 ワイヤレスインダクティブカップリングという技術を使用して、 チップ間のデータ通信を行うことができる3次元積層チップです。

ふんが研ではインダクティブカップリングを用いた三次元積層における効率の良いバスアーキテクチャの提案や、 実際にCMAやRISC-CPUの積層した三次元積層チップの実装を行っています。

従来のTSV技術と異なり、ワイヤレスによる通信が可能であるため、将来的に要求性能によって必要なチップを入れ替えるなどの柔軟性が期待されます。

いわば、チップのリコンフィギャラブルシステムです。

MuCCRA (動的リコンフィギャラブルプロセッサ)

-

MuCCRAという動的リコンフィギャラブルプロセッサの設計も行っています。

先ほどのCMAではアプリケーションが決まれば構成を変えずに演算を行いましたが、MuCCRAではアプリケーションの実行中に回路構成を変更することができます。

動的リコンフィギャラブルプロセッサは産業界に広く普及しており、我々も最新のプロセスを使って実チップの実装を行っています。

詳しくはこちらへ!

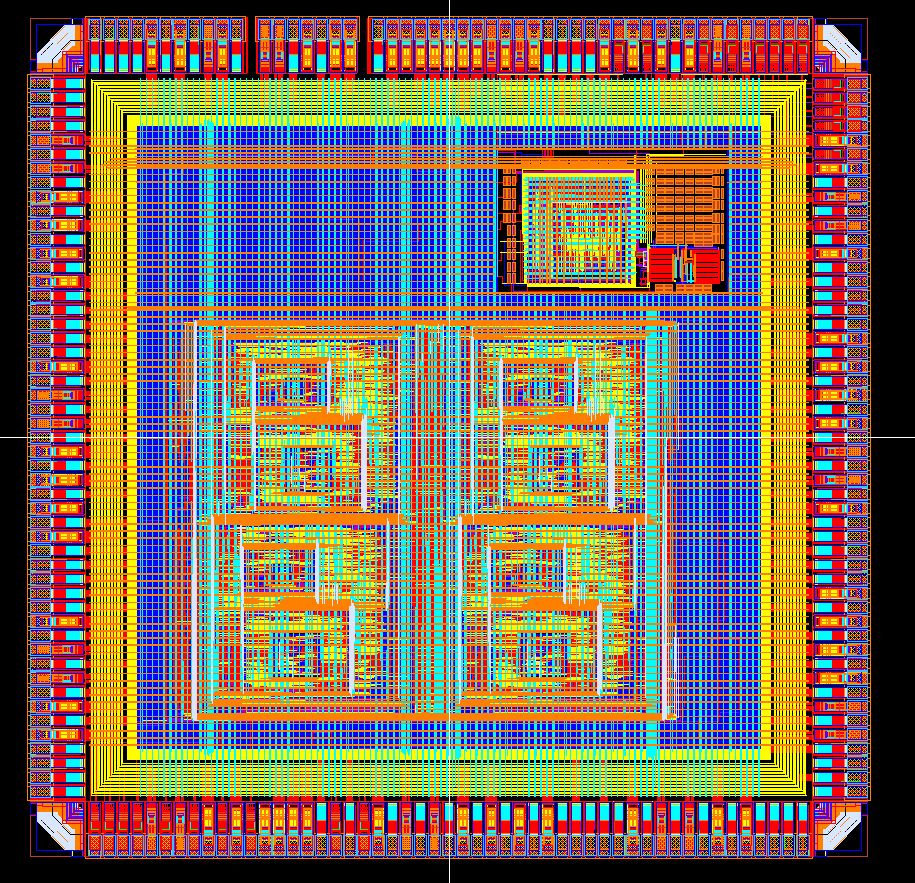

MuCCRAのレイアウト図 SOTB65nm FD-SOIプロセスを使用