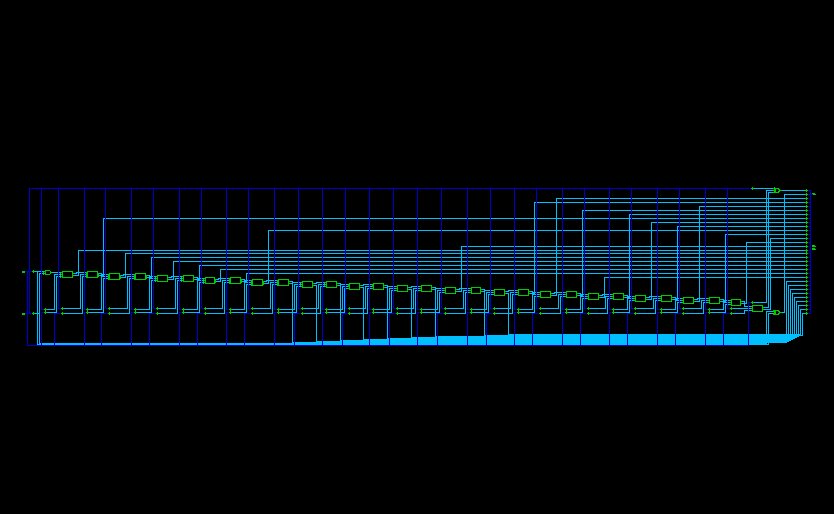

UX8L Design Compilerによる32bit加算器の論理合成手順

準備

/home/vdec/lib/ux8l/DesignFlow/sample_script/design_compiler

から,サンプルスクリプトをコピーする.

今回は,

/home/hlab/masayuki/wasmii3/ux8l/design_compiler/

にコピーをする.

attachedfileディレクトリをコピーして,ADDER32ディレクトリを作成する.

/home/hlab/masayuki/wasmii3/ux8l/design_compiler/ADDER32/verilog_rtl

に,新しいデザインファイルを置く.

今回は,ADDER32.vというデザインを作成した.

module ADDER32( CLK_IN, RESET_N, X_IN, Y_IN, Z_OUT ); input CLK_IN; input RESET_N; input [31: 0] X_IN, Y_IN; output [31: 0] Z_OUT; reg [31: 0] Z_OUT; always @ ( posedge CLK_IN or negedge RESET_N ) begin if( RESET_N == 1'b0 ) begin Z_OUT <= 32'h0; end else begin Z_OUT <= X_IN + Y_IN; end end endmodule // ADDER32

tclの修正

修正したtclを以下に置く.

- ADDER32_ux8l.tclhttp://www.am.ics.keio.ac.jp/~masayuki/ux8l/ADDER32_ux8l.tcl

- ADDER32_verilog_listhttp://www.am.ics.keio.ac.jp/~masayuki/ux8l/ADDER32_verilog_list

- ADDER32_const.tclhttp://www.am.ics.keio.ac.jp/~masayuki/ux8l/ADDER32_const.tcl

編集の概要

- ライブラリの場所の変更.ふんが研内でのライブラリの場所は,

/home/vdec/lib/ux8l

となる.

- いくつかのライブラリの追加,削除

これは dc_ux8l.setupにいくつかの変更を行っている.UX8L_w1_1.1V_MAX_primitive_lvt.dbの追加を行い,メモリまわり,PLL回りの不要そうなライブラリを削除.

- クロック制約の変更

ADDER32_const.tclにおいて,クロック制約の部分がなんだかよくわからなかったので,社長さん方式を導入.以下のようにクロック制約を書き換え.

create_clock -name "CLK" -period 5.0 -waveform {0 2.500} [find port {CLK_IN}]

- IOセルの制約の削除(ADDER32_const.tclの下の部分を全てコメントアウト)

これについては,IOセルについてまだよくわかってないから.また後で調べる.

論理合成

特に明示されていない限り、本Wikiの内容は次のライセンスに従います:CC Attribution-Noncommercial-Share Alike 3.0 Unported