以前のリビジョンの文書です

動的リコンフィギャラブルプロセッサとは

動的リコンフィギャラブル(動的再構成,Dynamically Reconfigurable)とは,アプリケーションの実行中に,その構成を変化させることのできるアーキテクチャです.具体的にどのような構成で,どのような仕組みでアプリケーションを実行していくのかについて解説します.

また,動的リコンフィギャラブルの利点についても解説します.

動的リコンフィギャラブルの特徴

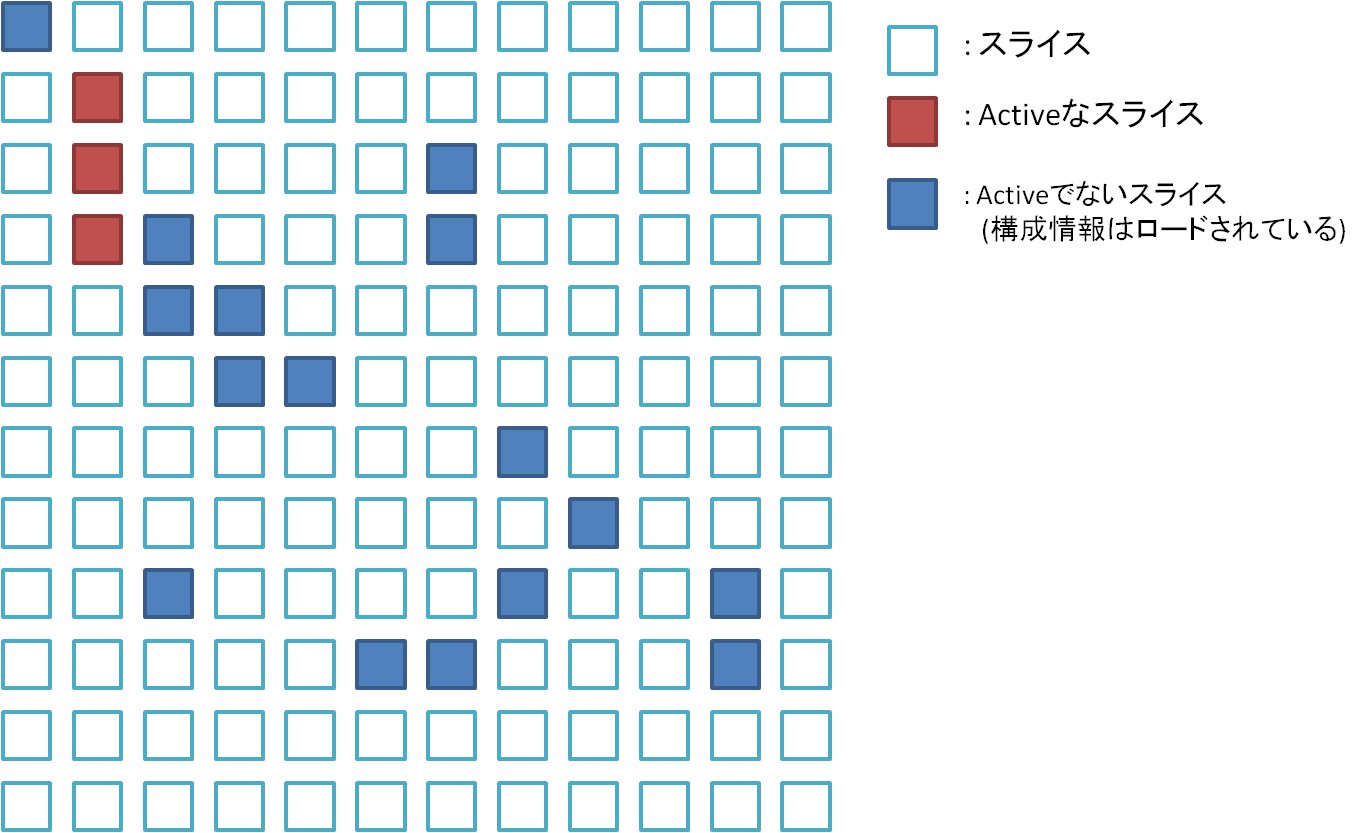

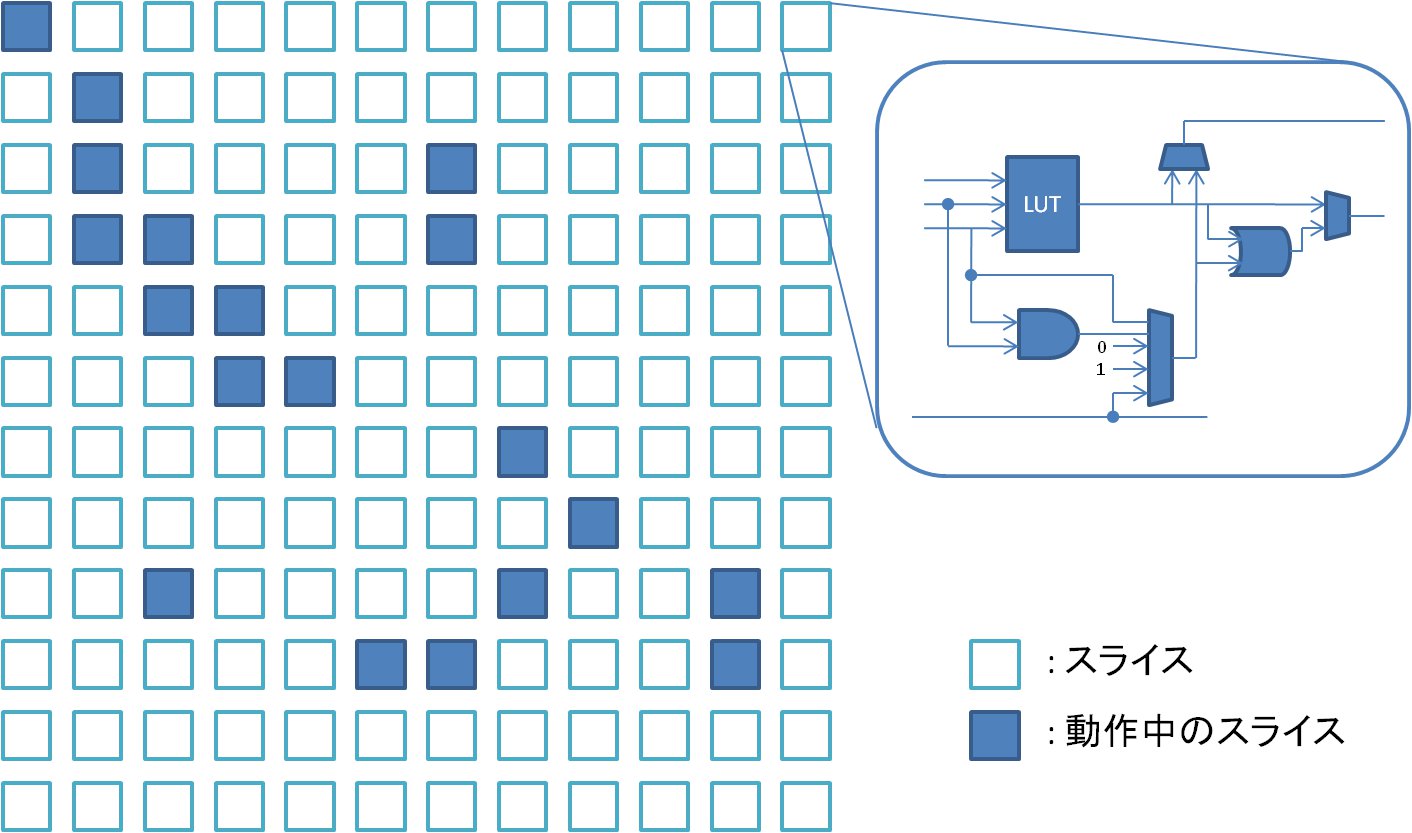

動的リコンフィギャラブルについて理解するためには,その対局にあるFPGA(Field-Programmable Gate Array)の構成についても理解する必要があります. FPGAは,実行前にアプリケーション(回路情報:コンテキストデータ)をロードします.実行が始まると,その回路構成は変化しません.回路構成を変化させることのできないFPGAは,規模の大きなアプリケーションを実行可能とするために,非常に大きな構造を取っています.サイズの大きいシリーズでは回路を構成するブロック(スライス)を何十万と搭載しており,大容量化するアプリケーションに耐え,さらには複数のアプリケーションを1チップのFPGAで実行できるようになってきています.

FPGAの構成(簡略図).スライスと呼ばれる回路構成単位を大量に並べた構成を取っている.

FPGAの構成(簡略図).スライスと呼ばれる回路構成単位を大量に並べた構成を取っている.

一方で,いくら大容量とはいえ,アプリケーション実行中には実行される領域は限られています.つまり,一瞬一瞬で考えると,アプリケーション回路をすべて安直に搭載すると非常に無駄があるわけです.