UX8Lのためのサンプルスクリプトを用いたレイアウトの手順

-1. はじめに

以下のレポートは,

/home/vdec/lib/ux8l/DesignFlow/Place_Rout_SampleScript_WEB-00465513-01.pdf

を参照して記述されている.ってか,ほとんどパクリである.

また,本レポートの作業ディレクトリは,

/home/hlab/masayuki/wasmii3/ux8l/

である.

0. 準備

A. 作業ファイルのコピー

論理合成によって生成したファイルを,(作業ディレクトリ)/pr/database以下にコピーする.

- (作業ディレクトリ)/design_compiler/MARIMOR2/gate/MARIMOR2_CHIP-compile.v を,(作業ディレクトリ)/pr/database/netlist/にコピー(リンク)する.

- ピン配置で生成したcsvファイルを,(作業ディレクトリ)/pr/database/pin_assign/にコピー(リンク)する.

- (作業ディレクトリ)/design_compiler/MARIMOR2/sdc_dc/MARIMOR2_CHIP.sdc を,(作業ディレクトリ)/pr/database/sdcにコピー(リンク)する.

以降,マニュアルを基本的に参照してほしい.独自に改変する必要がある場合のみ記述する.

B. lefファイルの作成

SOC Encounterを動作させるには,lefファイルというものを作成し,読み込ませなければならない.

(作業ディレクトリ)/pr/database/lef

にて,run_ace_lefcatを改変する.

### env

set path = ( $path \

/home/vdec/lib/ux8l/bin \

)

setenv OPC_PATH /home/vdec/lib/ux8l

setenv OPC_ADD /home/vdec/lib/ux8l/IO/OPC_ADD2

setenv OPC_PLL /home/vdec/lib/ux8l/PLL/linux

# setenv OPC_MEM

メモリのパスを消し,ベースとなるパスを変更する.

その後,本スクリプトを実行し,lefファイルを生成する.

C. VDEC_soce.confの作成

CONFIGファイルという,SOC Encounterを利用する際の必須ファイルを作成する. (作業ディレクトリ)/pr/database/conf/VDEC_soce.confを改変する.

# ============================================================================ # # --- Data preparation --- # # ============================================================================ # global DESIGN # Please change variables below set DESIGN MARIMOR2_CHIP # トップモジュール名 set OPC_PATH /home/vdec/lib/ux8l set OPC_ADD /home/vdec/lib/ux8l/IO/OPC_ADD2 set OPC_PLL /home/vdec/lib/ux8l/PLL/linux

1. フロアプラン

配置場所の定義を行う.

A. ile/fe_ini.tcl

set I_CNF ../../database/conf/VDEC_soce.conf # CONFIGファイルを指定 set I_LEF ../../database/lef/lef # lefファイルを指定 set I_NET ../../database/netlist/MARIMOR2_CHIP-compile.v # 論理合成後のネットリストを指定 set I_DEF ./io.def.gz set O_DEF ./floorplan.def.gz set O_NET ./floorplan.v.gz # set chipsize 2.5 # set chipsize 5.0 set chipsize 5025 # 5.0mm x 2.5mm のチップを利用

B. file/mkdef.tcl

set design MARIMOR2_CHIP # トップモジュール名 set pinassign_list ../../database/pin_assign/PAD_ASSIGN_MARIMOR2_UX8L_V03.csv # ピン配置ファイル set pad_file ../../database/pad_file/chip_5000x2500_FPBGA_pad.list # 5.0mm x 2.5mm のパッケージを利用 set output_def io.def.gz # set chipsize 2.5 # set chipsize 5.0 set chipsize 5025 # 5.0mm x 2.5mm のパッケージを利用 set iocell C0S8L0STARCIO_FE_TWF1IC33AS set plliocell C0S8L0STARCIO_FE_ACPLIO38V10 # set pllcell "C0S8L0STARCIO_FE_ACPLMPHH38V10 pll" # このセルはないので下記セルに変更 set pllcell "ACPLSCHL38V10 pll"

C. run_fec_floor

encounterを呼び出すためのスクリプトである.ふんが研では,SOC Encounterのパスは,

$ which encounter /home/vdec/cadence/SOC-8.1/tools/bin/encounter

なので,

############################################################# # set FEC = /eda_tools/cadence/soce_limited/08.10-e273_1/tools/bin/encounter set FEC = /home/vdec/cadence/SOC-8.1/tools/bin/encounter #############################################################

に改変する.以下,起動スクリプトは常にこのパスに書き換えること!!

スクリプト実行

普通にrun_fec_floorを実行する.floorplan.logにログが出力されるので,エラーが無いか確認すること.

2. 電源配線

省略.電源配線省略とか,死んでしまう。。。

3. 配置

A. file/place.tcl

あまり修正する部分はない.

# ============================================================================ # # --- Data preparation --- # # ============================================================================ # set inputConfig ../../database/conf/VDEC_soce.conf set inputVerilog ../01_floorplan/floorplan.v.gz # set inputDef ../02_proute/power.def.gz set inputDef ../01_floorplan/floorplan.def.gz set inputLef ../../database/lef/lef # set inputSDC ../../database/sdc/cpu8top_clock_200MHz.tcl set inputSDC ../../database/sdc/MARIMOR2_CHIP.sdc # Design-Compilerで出力したSDCファイルを指定 set outputVerilog ./place.v.gz set outputDef ./place.def.gz set dontuse ./file/dont_use.tcl

B. 配置実行

./run_placeを実行.

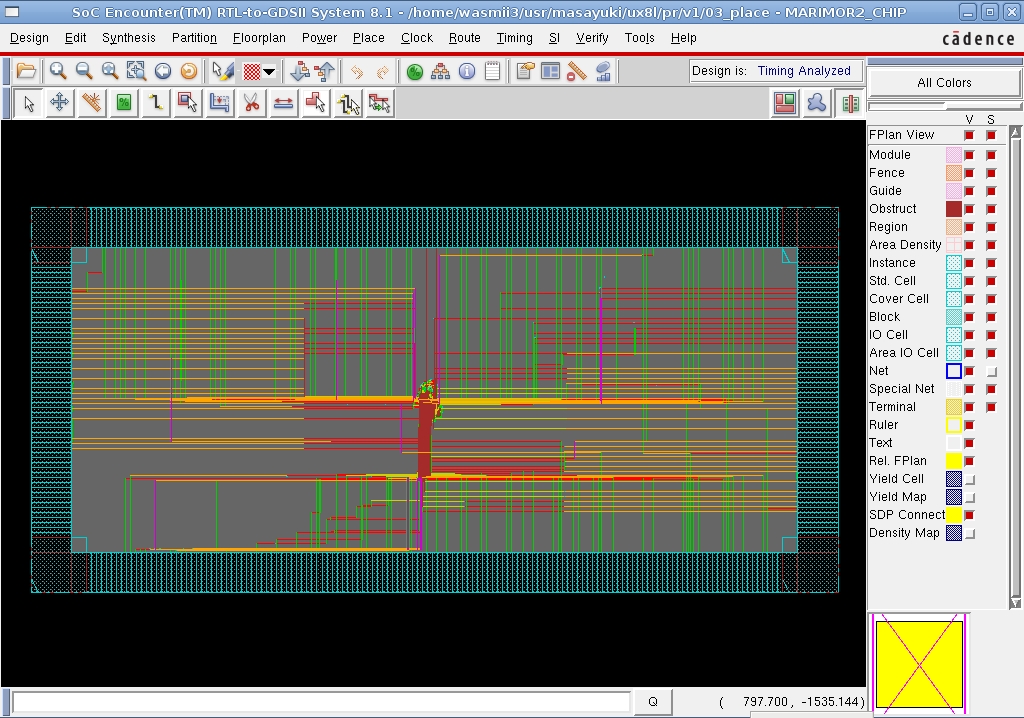

C. 配置結果

4. CTS(Clock Tree Synthesis)

クロックツリーを張る.

A. file/cts_spec

クロックの制約を記述したスクリプト.

### clock net name CLK # AutoCTSRootPin pll/CLKOUT AutoCTSRootPin IBUF_CLK_IN/Y # クロックのソースを指定 MaxDelay 8.0ns # 遅延制約を設定 # MaxDelay 4.0ns MinDelay 0.1ns MaxSkew 250ps NoGating NO Obstruction NO #LevelBalanced YES ForceMaxCap YES # MaxFanout 100 # ファンアウト制約を満たせなかったので,100->110に設定したが,いいのだろうか。。。 MaxFanout 110 # 100 -> 110 DetailReport YES #RootInputTran 0.2ns BufMaxTran 0.5ns SinkMaxTran 0.5ns RouteType clk_upper LeafRouteType clk_leaf #PostOpt YES #OptAddBuffer YES #OptAddBufferLimit 200 Buffer LDH_BUF_S_10 #LeafBuffer INVXP MaxCap + LDH_BUF_S_10 0.14pf #+ INVXP 0.11pf #+ GTDCLXP 0.11pf DefaultMaxCap 0.14pf CellHalo + LDH_BUF_S_10 6.666 0.550 #LeafPin #+ AAA/CCC/BE rising #+ BBB/CCC/BE rising #ExcludedPin #+ U_APLL_TOP/U360/B1 #+ U_APLL_TOP/U293/A #PreservePin #+ AAA/CCC/A #+ BBB/CCC/A #ThroughPin #+ BBB/DDD/CLK #PinMaxCap #+ AAA/BBB/Y 0.5pf #GatingGrpInstances #+ cg1/an cg1/i_0 #+ cg2/an cg2/i_0 #GatingGrpModule #+ grp_module1 #+ grp_a* End

B. cts.tcl

クロックツリーを生成するためのスクリプトである.

####################################################### #---------- Required setting by user ----------------- set inputConfig ../../database/conf/VDEC_soce.conf set inputDef ../03_place/place.def.gz set inputVerilog ../03_place/place.v.gz set inputLef ../../database/lef/lef # set inputSDC ../../database/sdc/cpu8top_clock_200MHz.tcl set inputSDC ../../database/sdc/MARIMOR2_CHIP.sdc # 論理合成時のsdcを指定する. set outputDef ./cts.def.gz set outputVerilog ./cts.v.gz #set ShieldNetList ./file/shield_net.list set clkSpec ./file/cts_spec set maxLayerNumber 7

#### replace root cell FCTS -> BUF setOptMode -rPlace set_dont_touch LDH_CTS false # set_dont_touch core/clk_blk/cts_clk1/CTS_ROOT false # set_dont_touch core/clk_blk/cts_clk2/CTS_ROOT false # set_dont_touch core/cts_reset/CTS_ROOT false set_dont_touch IBUF_CLK_IN false # クロックのdont_touch制約を解除 set_dont_touch IBUF_RESET_IN false # リセットのdont_touch制約を解除 # dbSetInstPlacementStatus [dbGetInstByName "core/clk_blk/cts_clk1/CTS_ROOT"] dbcPlaced # ecoChangeCell -inst "core/clk_blk/cts_clk1/CTS_ROOT" -cell "LDH_BUF_S_10" # dbSetInstPlacementStatus [dbGetInstByName "core/clk_blk/cts_clk2/CTS_ROOT"] dbcPlaced # ecoChangeCell -inst "core/clk_blk/cts_clk2/CTS_ROOT" -cell "LDH_BUF_S_10" # dbSetInstPlacementStatus [dbGetInstByName "core/cts_reset/CTS_ROOT"] dbcPlaced # ecoChangeCell -inst "core/cts_reset/CTS_ROOT" -cell "LDH_BUF_S_10" dbSetInstPlacementStatus [dbGetInstByName "IBUF_RESET_IN"] dbcPlaced ecoChangeCell -inst "IBUF_RESET_IN" -cell "LDH_BUF_S_10" # set_dont_touch core/clk_blk/cts_clk1/CTS_ROOT true # set_dont_touch core/clk_blk/cts_clk2/CTS_ROOT true # set_dont_touch core/cts_reset/CTS_ROOT true set_dont_touch IBUF_CLK_IN true # クロックのdont_touch制約を設定 set_dont_touch IBUF_RESET_IN true # リセットのdont_touch制約を設定

C. cts実行後の確認

cts実行後に,以下のファイルを確認する.

- cts.log : エラーが無いか確認すること

- cts.ctsrpt : クロックスキュー,およびViolationが存在しないことを確認すること.

- halo_check.rpt : “Failed : 0”となっていることを確認すること.

なお,cts.ctsrptでは,Violationが存在しない場合,CLK, RESETについて以下のようなレポートが出力されているはずである.

***** NO Max Transition Time Violation ***** ***** NO Min Transition Time Violation ***** ***** NO Max Capacitance Violation ***** ***** NO Max_Fanout Violation ***** ***** NO AC Irms Limit Violation *****

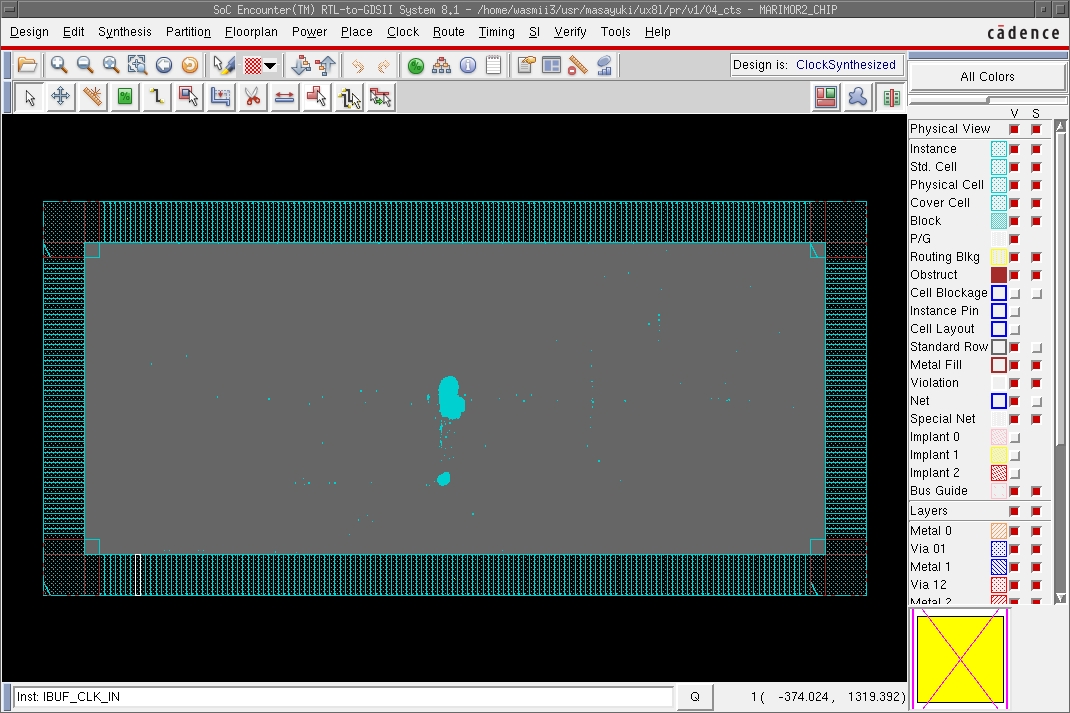

CTS実行後の結果.

5. 配線

ここで変更する部分はほとんどない.

今回はEncounterを起動せず,nanorouteというツールを用いてルーティングを行う. そのため,起動スクリプト./run_routeは次のようになっている.

if ( ! -f .routing_guide.rgf ) ln -s ../04_cts/.routing_guide.rgf .

#############################################################

# set NANO = /eda_tools/cadence/nano/8.1.e027/bin/nanoroute

set NANO = /home/vdec/cadence/SOC-8.1/tools/bin/nanoroute

#############################################################

${NANO} -64 -batch -init ./file/nanoroute_ux8l.tcl -log route.log

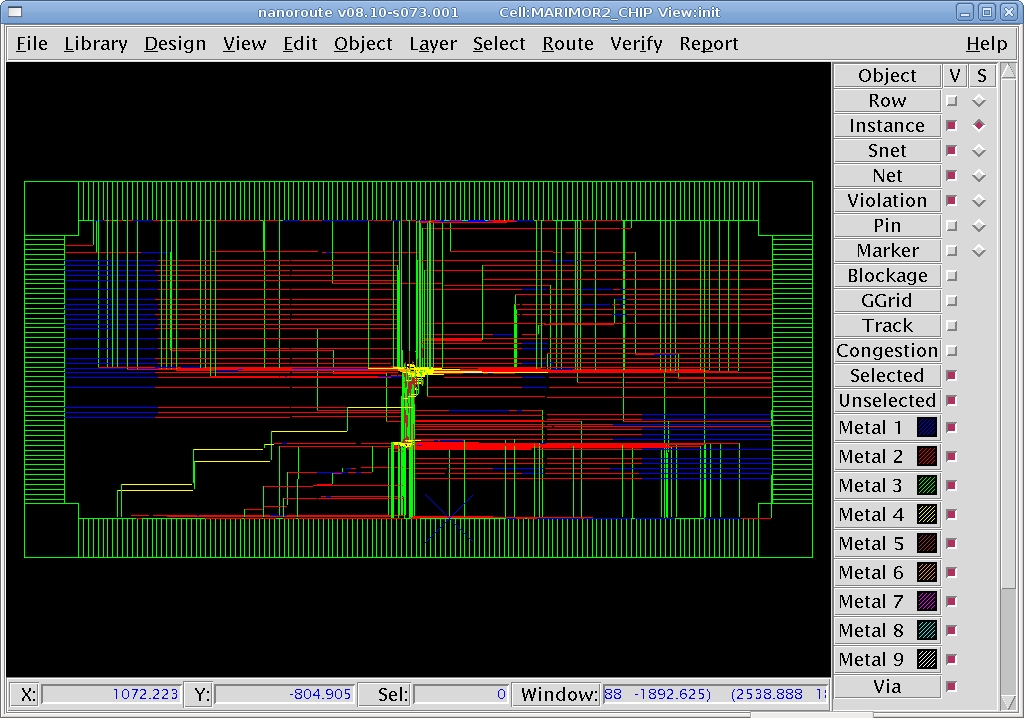

配線結果.ここではINDATA_27とINDATA_28にViolation Errorが出てしまっている.

Errorが発見された場合,MARIMOR2_CHIP_init_antenna.rptおよびMARIMOR2_CHIP_init_vialation.rptにエラーメッセージが出てくるはずである.今回はこのようになっている.

- MARIMOR2_CHIP_init_antenna.rpt

Total number of net violated process antenna rule = 0.

- MARIMOR2_CHIP_init_violation.rpt

Begin violation report:

Design Rule VIOLATION: NET (W_IDATA_IN_27_), LAYER (M1L)

location (160.710000 -917.796000), type (VERTICAL)

Design Rule VIOLATION: NET (W_IDATA_IN_28_), LAYER (M1L)

location (190.806000 -917.796000), type (VERTICAL)

End violation report

どうやったら消せるの…

6. シールド配線

クロック配線に対して,シールドを行う.

基本的に,tclには変更する部分は無し.

- ./run_shield_attribute

- ./run_shield

のふたつを実行する.

7. メタル埋め

メタル密度基準を満足するためにメタルを埋める.

A. file/metal_fill_ux8l.tcl

いくつかのコード修正を行う.

set inputConfig ../../database/conf/VDEC_soce.conf set inputLef ../../database/lef/lef set inputDef ../06_shield/shield.def.gz set inputVerilog ../04_cts/cts.v.gz # set chipsize 2.5 #set chipsize 5.0 set chipsize 50.25 # チップサイズに応じてオプションを変更する. #set inputECOFile <input ECO file>

さらに注意すべき点として,addMetalFillの修正を行う.![]()

![]() 無効なオプションが入っているので,これを消去する.これを行わないとメタルが入らないので,注意!!

無効なオプションが入っているので,これを消去する.これを行わないとメタルが入らないので,注意!!

# modified by Masayuki KIMURA

# useNonDefaultSpacing is not defined in addMetalFill

addMetalFill -iterationNameList { step1 step2 } -extraConfig cont.conf \

-layer { 1 2 3 4 5 6 7 } -area $X1 $Y1 $X2 $Y2 \

-timingAware on -snap -onCells -stagger off

# addMetalFill -iterationNameList { step1 step2 } -extraConfig cont.conf \

# -layer { 1 2 3 4 5 6 7 } -area $X1 $Y1 $X2 $Y2 \

# -timingAware on -snap -onCells -stagger off \

# -useNonDefaultSpacing

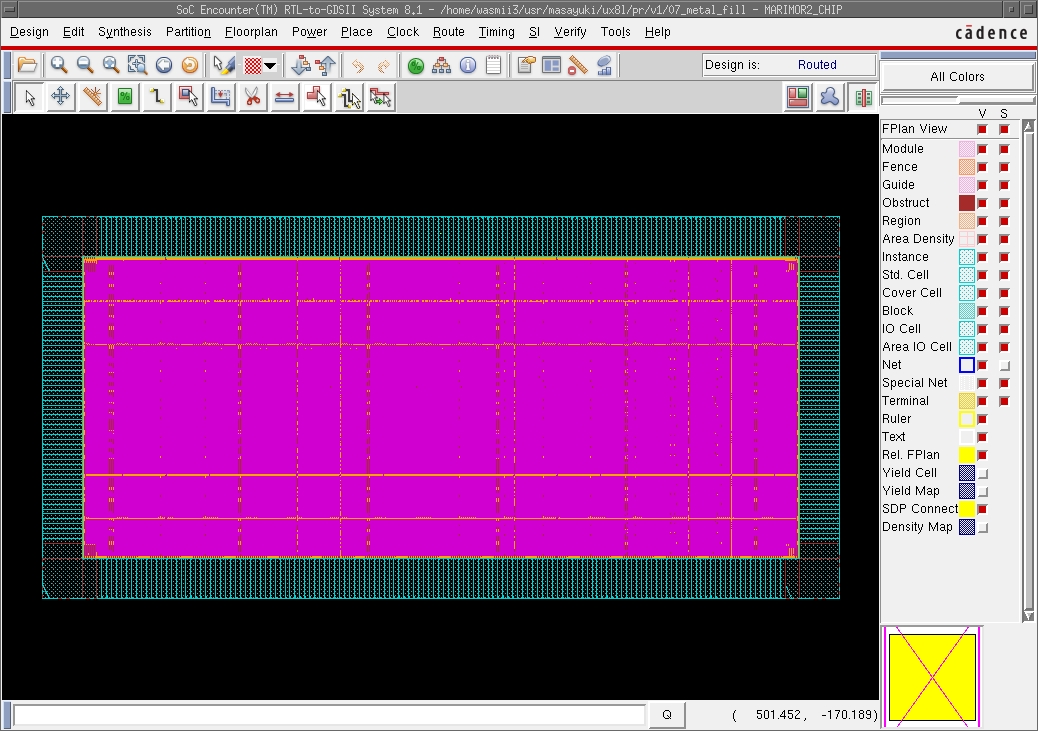

実行結果.

実行結果の確認

実行後,以下のファイルの内容を確認し,全てにおいて”No density violations were found.”と記述されていることを確認する.

- metal_density_final1_max.rpt

- metal_density_final1_min.rpt

- metal_density_final2_max.rpt

- metal_density_final2_min.rpt

- metal_density_final3.rpt

8. デカップリング容量セル埋め

デカップリング容量セルの挿入.これも変更点は少ないが,一点ほど,制約ファイルの変更がある.

A. file/cdfill_soce.tcl

set ENCOUNTER_VERSION 8.1 set SOCE_VER 08.10-e296 set TECHNOLOGY UX8L #set DESIGN <design name> ; # Specify in the config file set inputConfig ../../database/conf/VDEC_soce.conf set inputVerilog ../04_cts/cts.v.gz set inputDef ../07_metal_fill/metalfill.def.gz set inputLef ../../database/lef/lef set inputSDC ../../database/sdc/MARIMOR2_CHIP.sdc # sdcファイルを論理合成時に出力したものに置き換える

9. フィルセル埋め

デカップリング容量セルが挿入できなかった場所を,フィルセルで埋める.

スクリプトは,変更を行う場所は無し.

10. Verify

SOC Encounterを用いて,デザインのベリファイを行う.

これもスクリプトに変更点は無し.

ところが,Verify実行後に,大量のGeometry Errorが出る.

例えばこんなの.

SHORT: Pin of Cell FILL_F__impl4_900865 & Blockage of Cell NECTLBUFF ( M1 ) Bounds : ( -2181.828, 904.563 ) ( -2181.795, 904.629 )

原因不明.なんじゃこりゃ.