8ビットカウンタのAstroによるレイアウト奮闘記

レイアウトサイズの設定

Design Compilerによるレポートが,

Total cell area: 3969.000000 Total area: undefined

だったので,100×60くらいで設定.

set core_width 100.0 set core_height 60.0

セルの高さとかも,ビビってマニュアル通りに

set cell_width 101.8 // core_width + 1.8 ? set cell_height 61.8 // core_height + 1.8 ? set core_to_top 0.9 // 0.9 はセルの高さの半分 set core_to_bottom 0.9 set core_to_right 0.9 set core_to_left 0.9

VerilogToCell

TLUの設定

- apply_tlu_plus.tcl

ロームのライブラリを使ったときにクソはまった部分.なぜだかROHMのライブラリではITFファイルをきちんと読み込めない.

しかたがないのでf65で全部やることにした.

TDFファイルの読み込み

- load_tdf.tcl

TDFファイルとは,入出力ポートをマクロのどこに置くかを設定する.

ここらへんセンスが問われる.別のIOポートと結ぶときに,逆側からビヨーンって線を伸ばしたらかっこわるいもんね.

僕はこんなTDFファイルを作った.ぶっちゃけ,社長さんのパクリである.

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; ; ; ./tdf/COUNTER8.tdf ; ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; ;; TOTAL : 10 ;; NORTH : 0 ;; SOUTH : 0 ;; EAST : 8 ;; WEST : 2 ;;;;;;;; WEST (2) ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; pin "CLK" "MET2" 0.1 0.1 "RIGHT" 1 pin "RST_N" "MET2" 0.1 0.1 "RIGHT" 2 ;;;;;;;; EAST (8) ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; pin "COUNTER_OUT[0]" "MET2" 0.1 0.1 "LEFT" 1 pin "COUNTER_OUT[1]" "MET2" 0.1 0.1 "LEFT" 2 pin "COUNTER_OUT[2]" "MET2" 0.1 0.1 "LEFT" 3 pin "COUNTER_OUT[3]" "MET2" 0.1 0.1 "LEFT" 4 pin "COUNTER_OUT[4]" "MET2" 0.1 0.1 "LEFT" 5 pin "COUNTER_OUT[5]" "MET2" 0.1 0.1 "LEFT" 6 pin "COUNTER_OUT[6]" "MET2" 0.1 0.1 "LEFT" 7 pin "COUNTER_OUT[7]" "MET2" 0.1 0.1 "LEFT" 8

ピンガイドの設定

- pin_guide.tcl

ブロッケージをマクロの端に入れる.やってみたものの,あんまり意味ねー?

ちなみにガイドは,ガイドさんのガイドというよりも,柵の様なガイドのイメージ,だと思う.

ちなみに,QandAの方にも書いたが,これはしゃちょ様のアンテナ対策であり,やらなくてもいいらしい.

さらに,次のanntena_route_guide.tclも同様にやる必要無し.ふんがさん曰く,「おまじない」

anntena_route_guide.tclがやっていること.

アンテナとは,長すぎる配線を作るとでるエラーのこと.だから,長い配線を作らないために,ちょっと行ってはレイヤを変え,ちょっと行ってはレイヤを変えを 繰り返す.

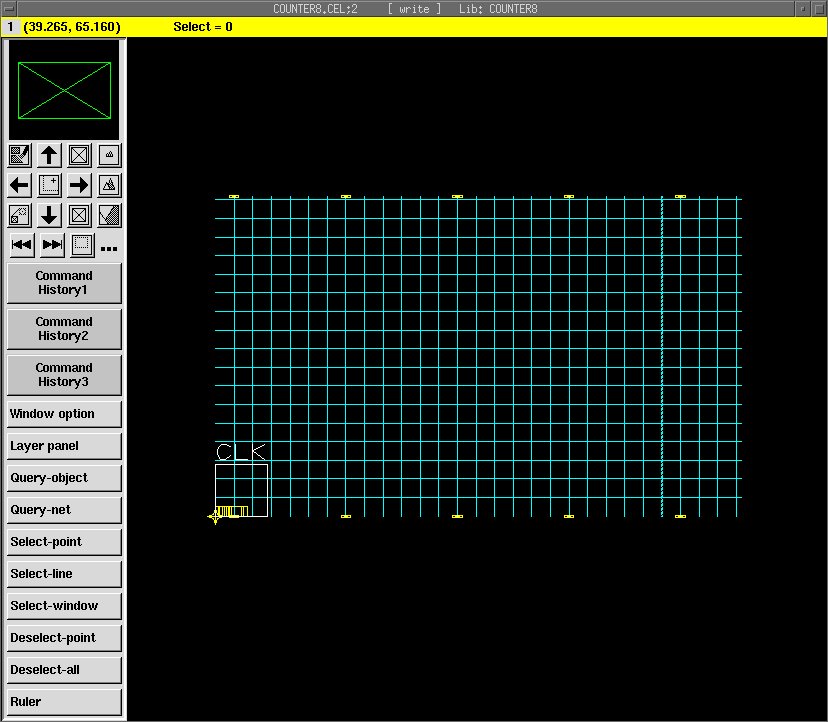

これを強制的にやるために,しゃちょ様は,少しずつ(3.6ずつ)ずらしながら配線禁止エリアを設定し,3.6ごとに無理矢理レイヤを変えるように設定しているのか!

######## VERTICAL ROUTE GUIDE ##################################

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m3 1

formHide add_route_guide

for {set x 3.6} {$x < $cell_width} {set x [expr $x + 14.4]} {

addPoint 1 [concat $x 0 ]

addPoint 1 [concat [expr $x + 0.01] [expr $cell_height]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m5 1

formHide add_route_guide

for {set x 7.2} {$x < $cell_width} {set x [expr $x + 14.4]} {

addPoint 1 [concat $x 0 ]

addPoint 1 [concat [expr $x + 0.01] [expr $cell_height]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m7 1

formHide add_route_guide

for {set x 10.8} {$x < $cell_width} {set x [expr $x + 14.4]} {

addPoint 1 [concat $x 0 ]

addPoint 1 [concat [expr $x + 0.01] [expr $cell_height]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m9 1

formHide add_route_guide

for {set x 14.4} {$x < $cell_width} {set x [expr $x + 14.4]} {

addPoint 1 [concat $x 0 ]

addPoint 1 [concat [expr $x + 0.01] [expr $cell_height]]

}

abortCommand

見た目は同じ線でも,隣同士2段ずつレイヤが違っている.うわー,こまけー.

######## HORIZONTAL ROUTE GUIDE ################################

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m2 1

formHide add_route_guide

for {set y 3.6} {$y < $cell_height} {set y [expr $y + 14.4]} {

addPoint 1 [concat 0 $y ]

addPoint 1 [concat [expr $cell_width] [expr $y + 0.01]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m4 1

formHide add_route_guide

for {set y 7.2} {$y < $cell_height} {set y [expr $y + 14.4]} {

addPoint 1 [concat 0 $y ]

addPoint 1 [concat [expr $cell_width] [expr $y + 0.01]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m6 1

formHide add_route_guide

for {set y 10.8} {$y < $cell_height} {set y [expr $y + 14.4]} {

addPoint 1 [concat 0 $y ]

addPoint 1 [concat [expr $cell_width] [expr $y + 0.01]]

}

abortCommand

axgAddRouteGuide

formDefault "Add Route Guide"

setFormField add_route_guide no_signal_route_on_layer: 1

setFormField add_route_guide m8 1

formHide add_route_guide

for {set y 14.4} {$y < $cell_height} {set y [expr $y + 14.4]} {

addPoint 1 [concat 0 $y ]

addPoint 1 [concat [expr $cell_width] [expr $y + 0.01]]

}

abortCommand

フロアプラン

- floorplan.tcl

僕は,「コアエリア」を作るものだと理解している.チップは2つのエリアから構成される.

- パッド・エリア

- コア・エリア

で,パッドエリアは,チップの端の方にあるIOピンを置く所.コアエリアはまんなかの実際にレイアウトする部分.

で,floorplan.tclは,コアエリアがどこにあたるのかを示している.具体的には,セルから0.9だけ奥に入った所になっている.ってかそういう風に指定している.

あれ,でも今ルーラで計ってみたら横方向は0.9だけど縦は1.0あるぞ.まあいいや.

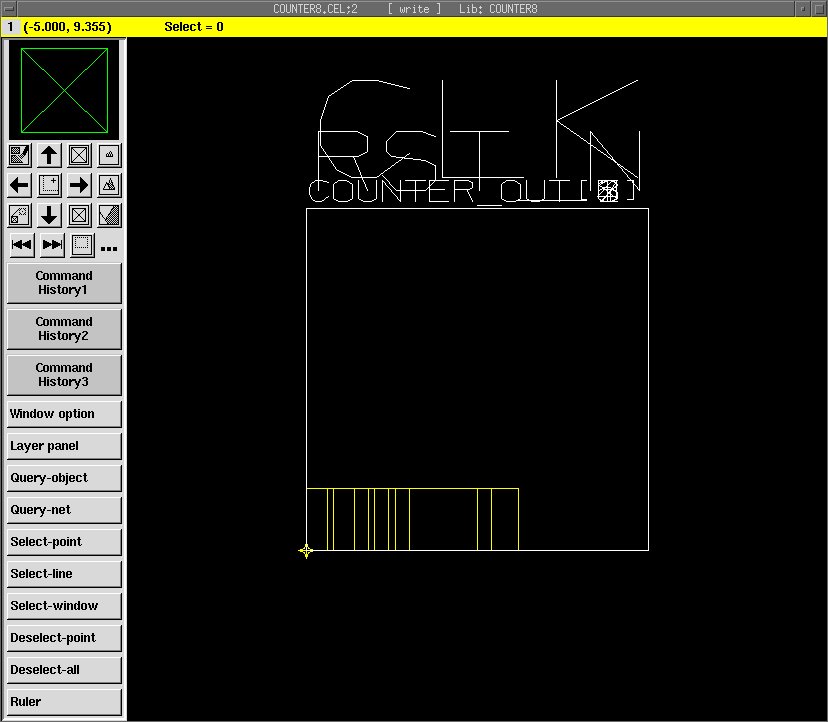

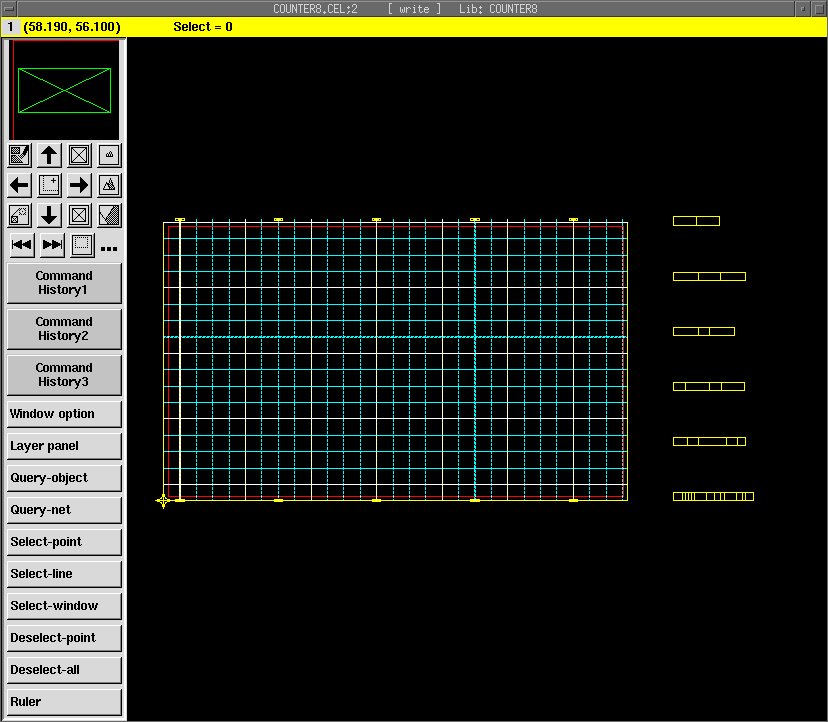

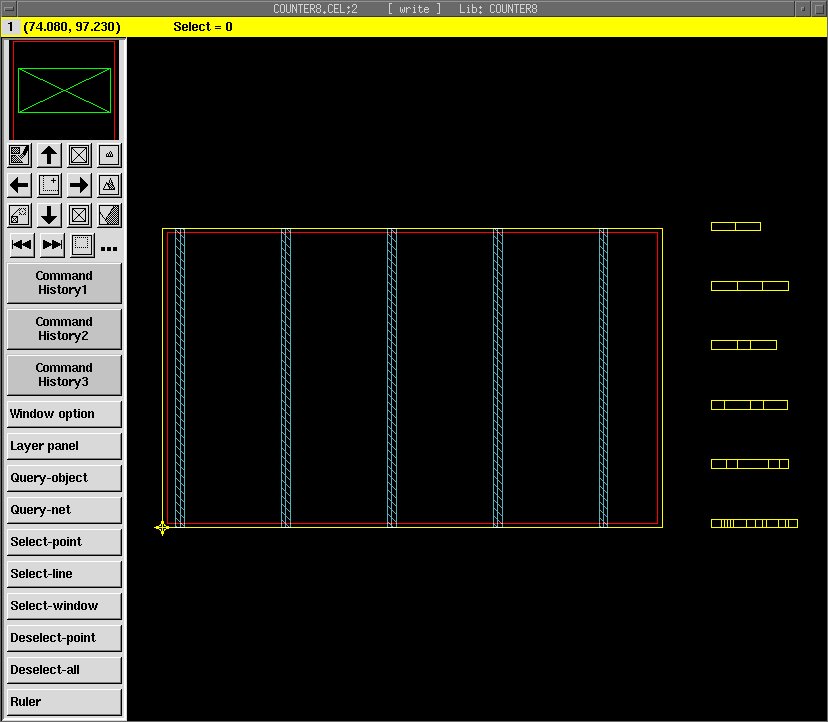

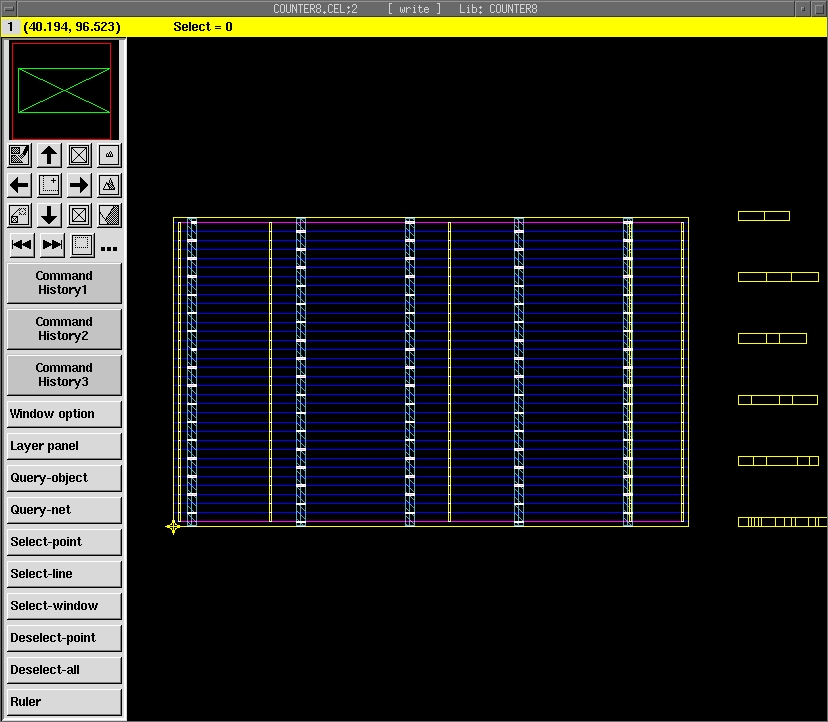

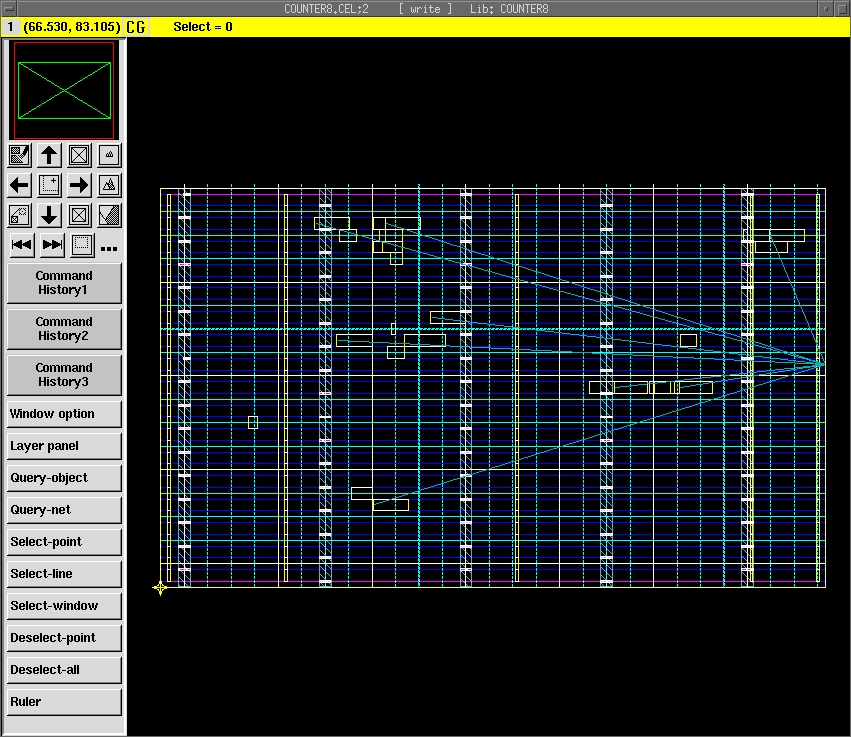

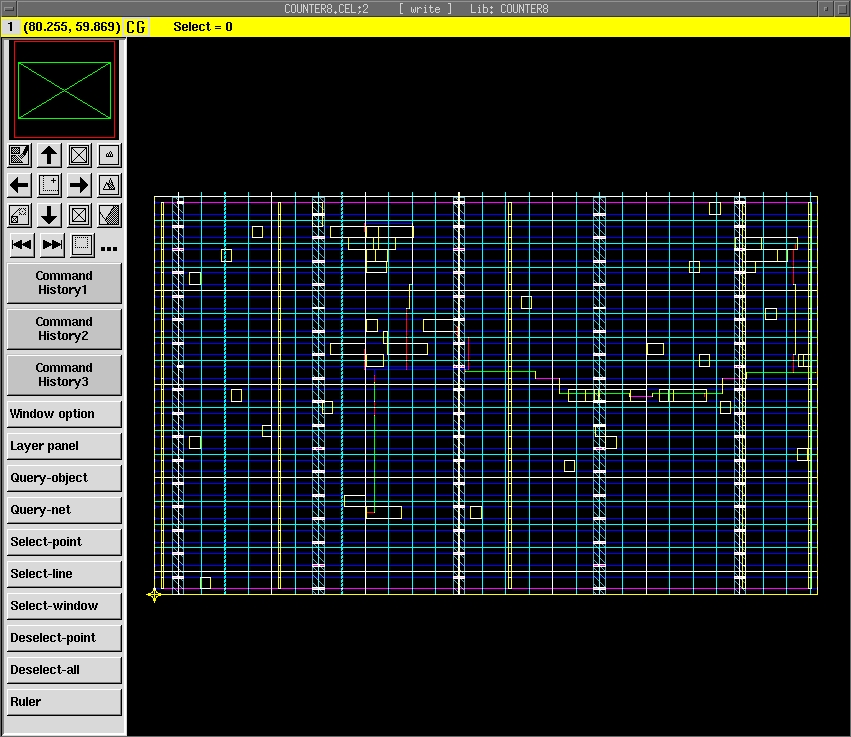

フロアプラン後の結果.マクロの内側に赤いラインができている.これがコアエリア?

まだセルは配置されてないけど,これはplacementで配置される.よかったー.

デザインチェック

- check_design.tcl

ここでちょっと休憩.デザインチェックを行う.astCheckDesignというのがあるんだねー.便利.レポートは./rptに作られる.mkdirしとかないと怒られた.

ちなみに,レポートはこんな感じで出てきた.くっそ長い.

Tool: Astro

Version: Z-2007.03-SP7 for IA.32 -- Feb_20,_2008

Design: COUNTER8

Limits: 1 res=10.0000 area=20.0000 tran=1.0000 cap=1.0000

Info:

Nets:

clock clock net

drivers=%d multi driver net with num drivers

bi net connects to bidirectional port

tri net connects to tristate port

def net assigned default delay/tran/cap

ndt net assigned as dont touch

nonprop net is non-propagated for delay

tran net has a transition violation

cap net has a capacitance violation

nobrk net cannot be broken by optimization

Masters:

DU cell assigned as dont use

DT cell assigned as dont touch

CLK cell assigned as clock cell

DLY cell assigned as delay cell

Current Include Interconnect Timing:

PDSSUM: Setup (Target=0.1000) Hold Num Num

PDSSUM: Slack Num Total Slack Num Trans MaxCap

PDSSUM: 10000.000 0 0.0 10000.000 0 102 0

Current Ignore Interconnect Timing:

PDSSUM: Setup (Target=0.1000) Hold Num Num

PDSSUM: Slack Num Total Slack Num Trans MaxCap

PDSSUM: 10000.000 0 0.0 10000.000 0 96 0

Design Information:

Cell Instances: 30

Macro Instances: 0

Pins: 10

Nets: 35

Hierarchy Preservation: Exists

Perserving 0 of 1 hierarchical instances

*** Hierarchy preservation degrades optimization results

ScanChainConnections: Not Found

...

Blockage, RouteGuideの取り外し

- remove_blockage.tcl

- remove_route_guide.tcl

ブロッケージを取り外す.tclの中にあるgeGetEditCellとは,

Returns the cell ID of a cell open in the current layout window.

のことである.訳すのめんどい.

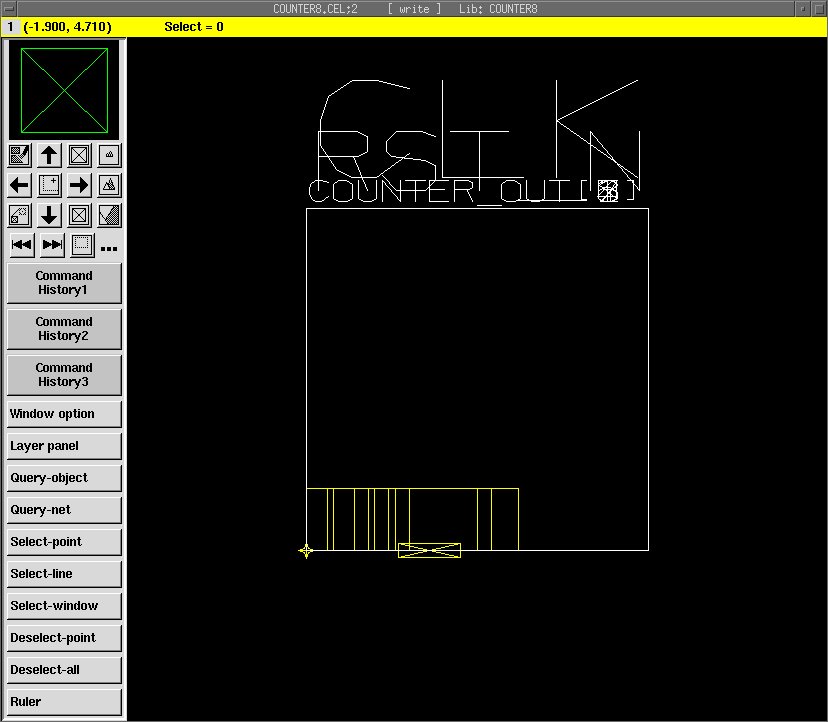

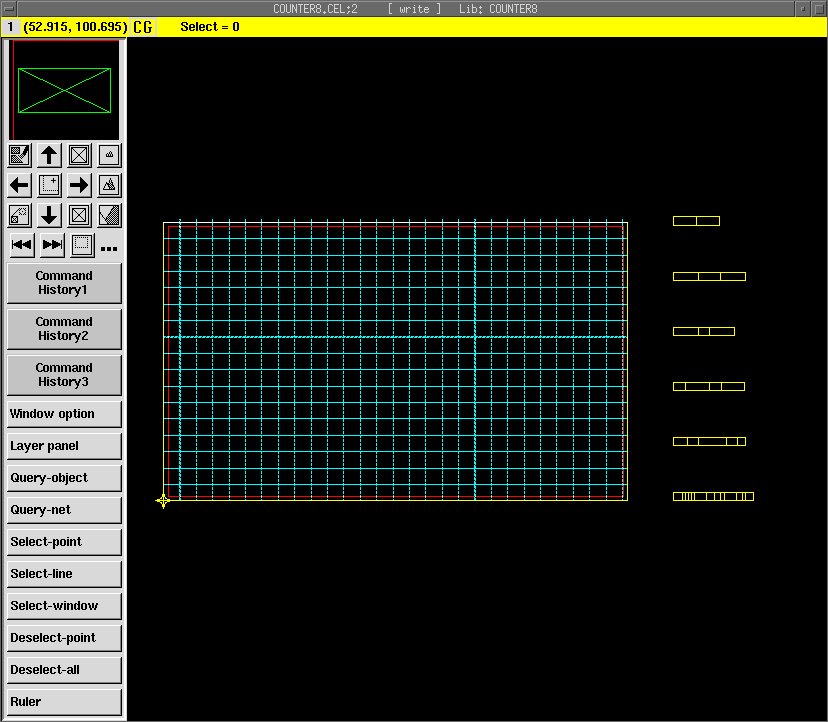

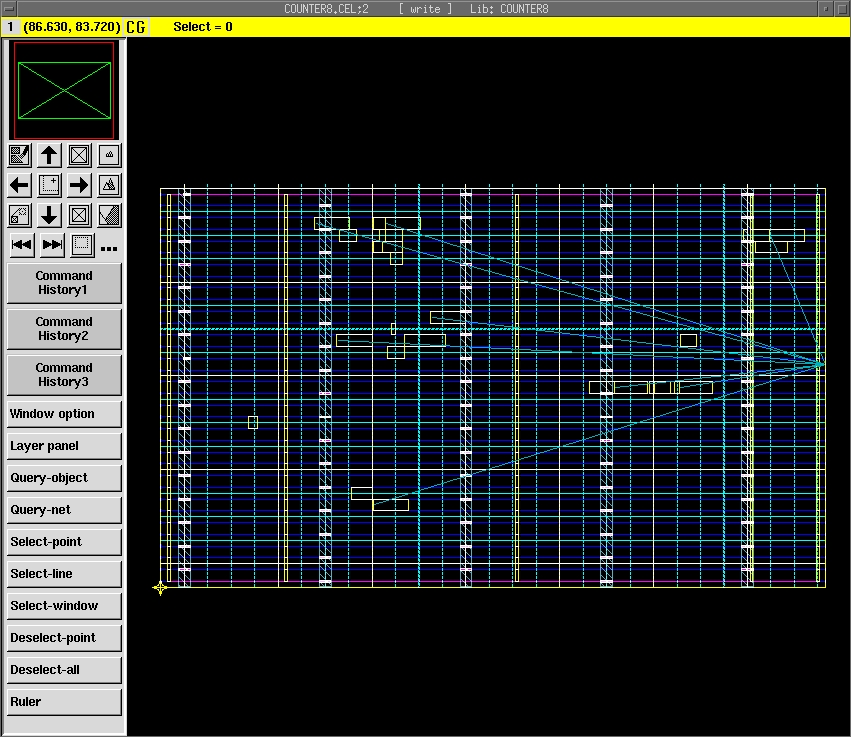

ほら,ちょっときれいになった.

調子に乗ってルートガイドも取り外す.axDeleteAllRouteGuideとは,デザイン中の全てのルートガイドを削除するコマンドである.そのままじゃん.

データタイミングチェック

タイミングをチェックする.これもレポートが出てきて,Unconstrained Endpointsがわんさか出てくるが,これはそもそも指定していないで大丈夫,だと思う.

PGコネクト

マクロ間とか,ポート間で電源配線をつなぐためにやってるのかな?1つのマクロだけだと変化が無いのかも.

話を聞いてみると,電源とグランドを「論理的に」認識させているらしい.つまり「このポートが電源」で「このポートがグランド」だという事を認識させている.

至るところで出てくるが,少しでもマクロを移動すると電源として認識されなくなるのでビビってやっているらしい.

一時保存

- save_cell.tcl

休憩.GNOME上海でもやろう.まあ保存自体は超高速に終わるけど.

route strap

route rail

- route_rail.tcl

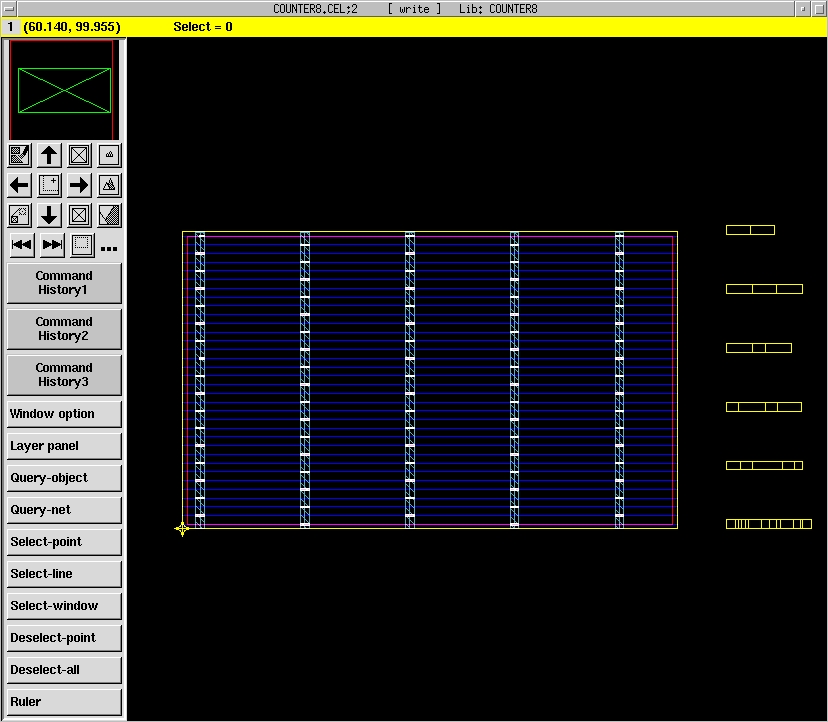

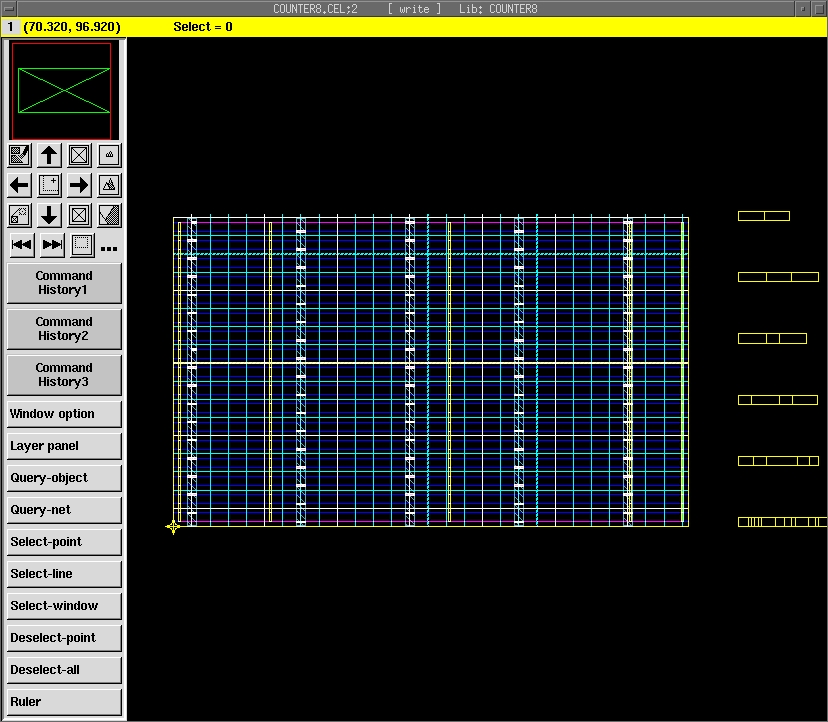

ストラップが縦方向なら,レールは横方向である.

張るレイヤも違う(当たり前).ストラップがMET6,レールがMET11.

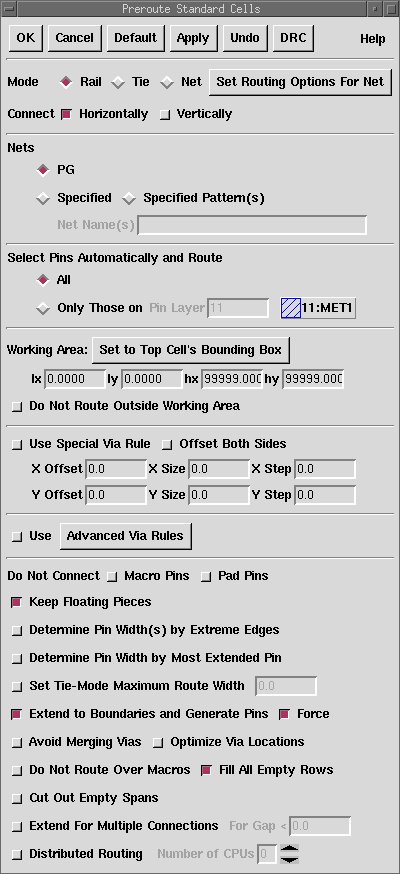

最初axgPrerouteStandardCellsというコマンドはなんの事だか分からなかったが, 画面を見ると普通に「Rail」モードになっている.なーんだ.

“Extend to Boundaries and Generate Pins”をチェックするのがポイント.マニュアルには,トップセルでは無く,パッドが存在しないときはこのオプションを有効にせよと書いてある.

このオプションを利用すると電源とグランドがセルの境界にまで引き伸ばされて,電源とグランドピンが作られる.

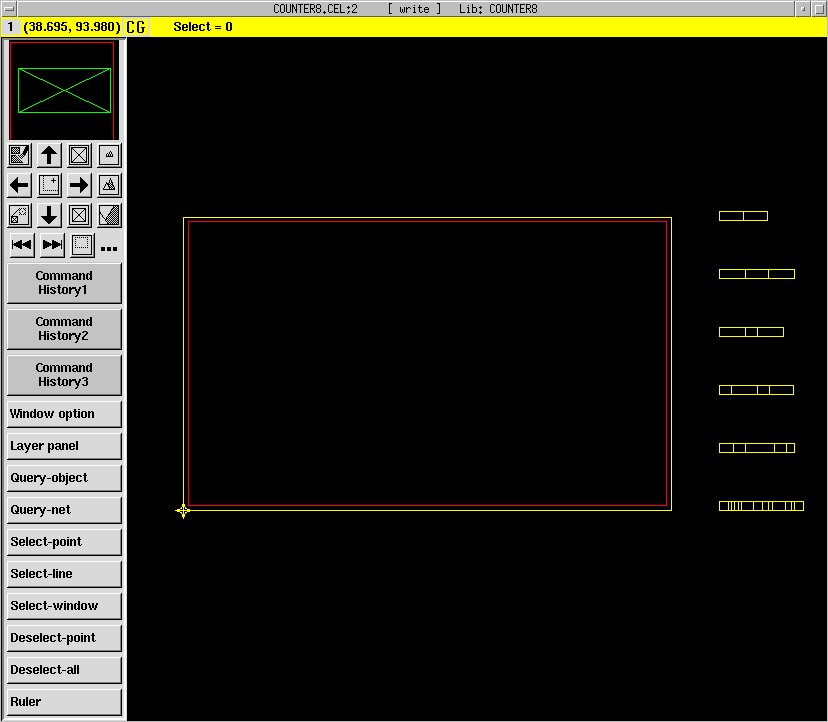

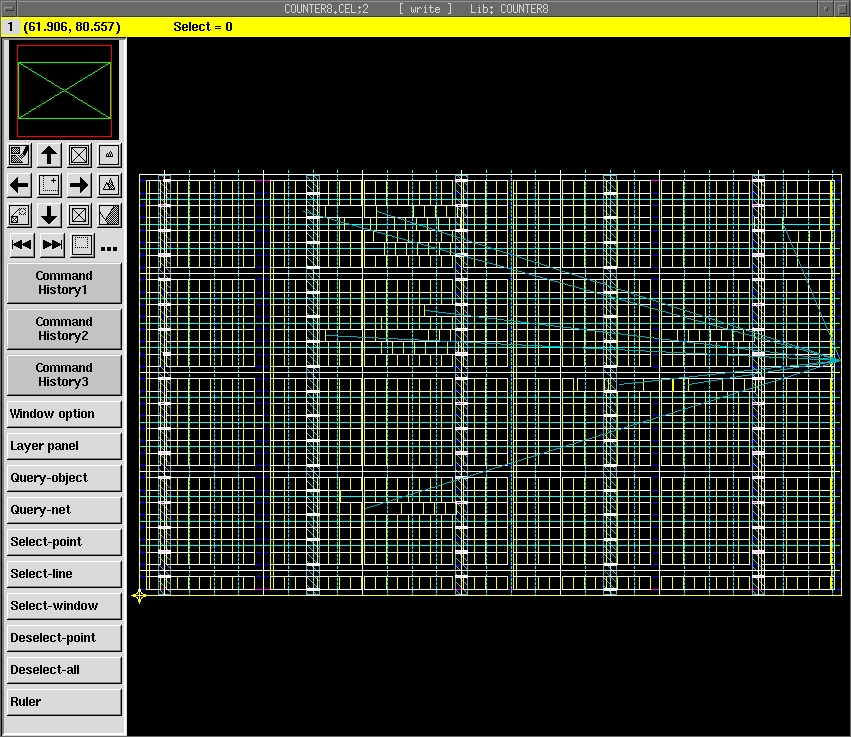

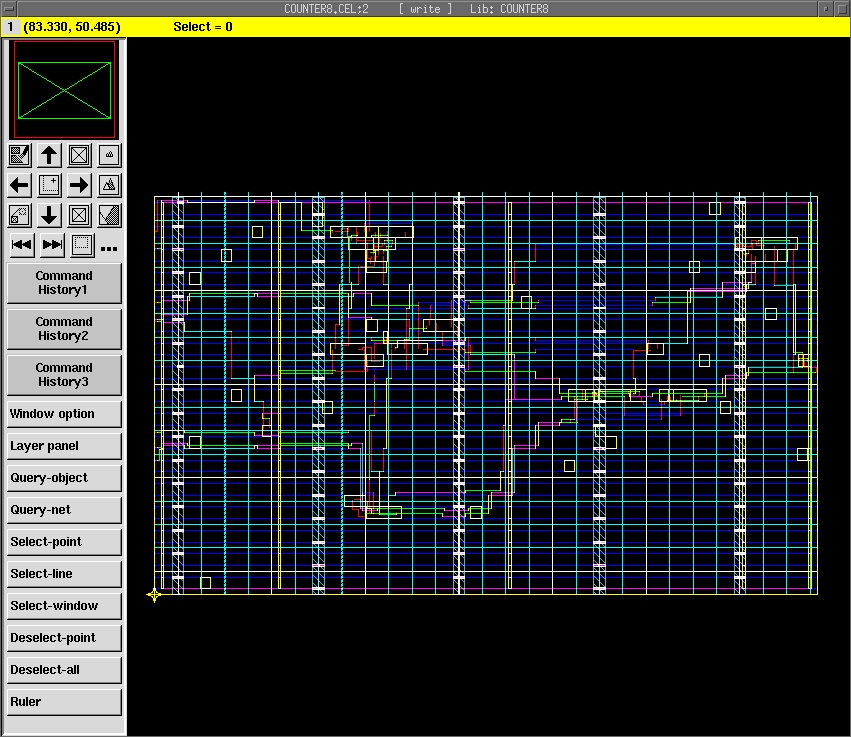

レールを張った結果.

tapの挿入

- insert_tap_array.tcl

CMOS VLSI Designを読むと,ラッチアップという現象を防ぐために,substrate tap, well tapを挿入するらしい.Fujitsuのライブラリの資料にも挿入せよと書いてあったぞ.

よくわからんけど,とりあえず今は挿入するもんだということにしておこう.

insert_tap_array.tclを読むと,最初に

axSetIntParam "apl" "tapCellUniformPlacement" 1

と書いてある.マニュアルで調べると,タップセルを等間隔で配置して,マクロが存在する列もマクロを避けて配置するためには,axgArrayTapCellが必要らしい.それで書いてあるのか.

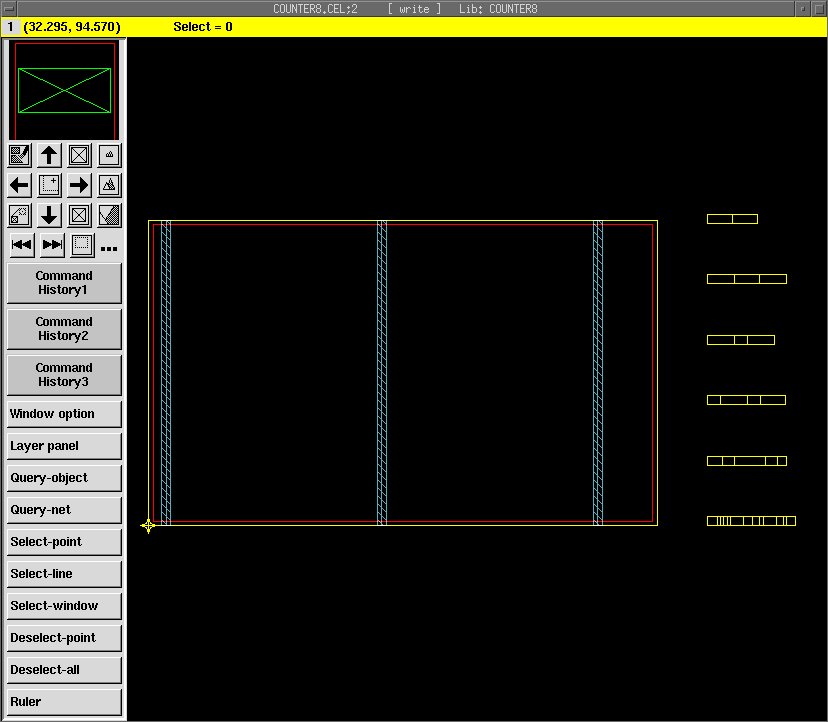

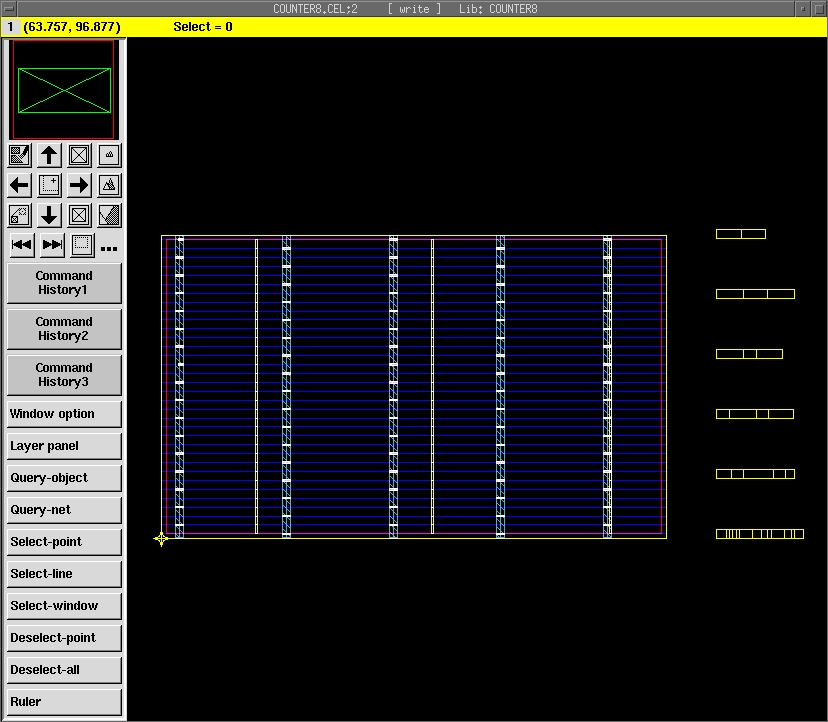

タップセルが入ったー.

最後に,

axAddEndCap [geGetEditCell] SC23YUZTAP021 0 0 1 0

とやる.そうすると,右端と左端に同様にタップセルが挿入される.

もう一度アンテナルートガイドの設定

SDCのロード

- load_sdc.tcl

SDCとは,SYNOPSYS Design Constraints formatで,Design Compilerで論理合成したときに出力される.タイミング制約のファイルの種類である.

ataRemoveTCで,タイミング制約を取り除く.詳しくはマニュアルを読むべし.

ataLoadSDCで,SDCを読み込む.これをMilkyWayデータベースに取り込む.

最後に,ataWriteTCでSDCを書き込む.

CTSのタイミングセットアップ

- pre_cts_timing_setup.tcl

いろいろ指定する.これについてはまた調べる.

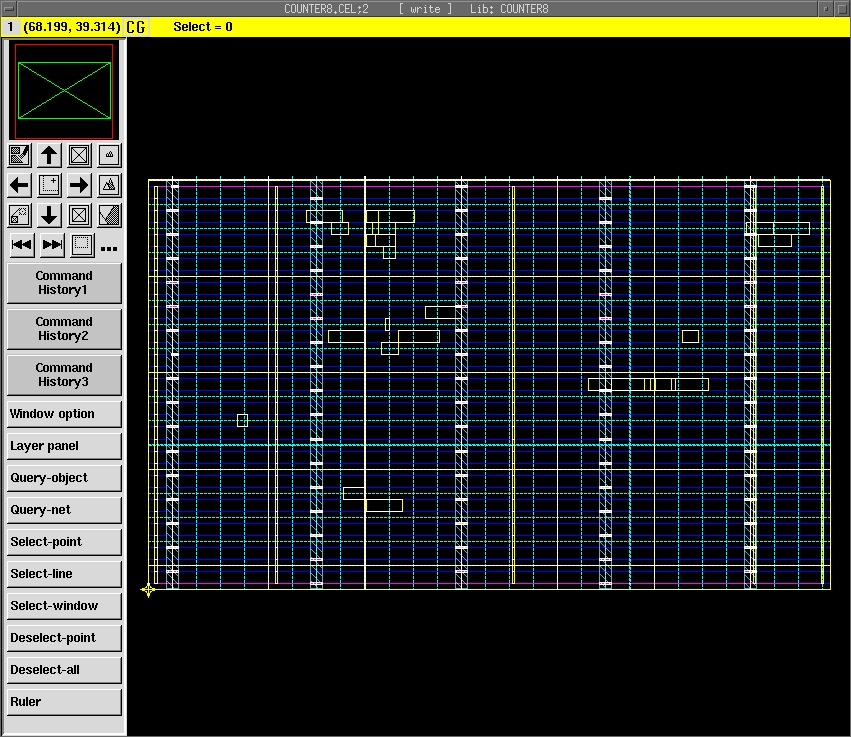

配置

- auto_place.tcl

いよいよだ.

axSetIntParam "pds" "more_loc_in_ppo" 1

いきなり,よくわからん.

pdsHFNCollapse 10

マニュアルには,バッファがいっぱいあるときは,有効だと書いてある.ファンアウトの最大値が10になるらしい.

pdsHFNCollapseは,マニュアルによると,バッファやインバータの数を減らして,混雑度を減らすらしい.

astPlaceOptions astAutoPlace

これで配置開始.詳細についてはあまり見ていない.

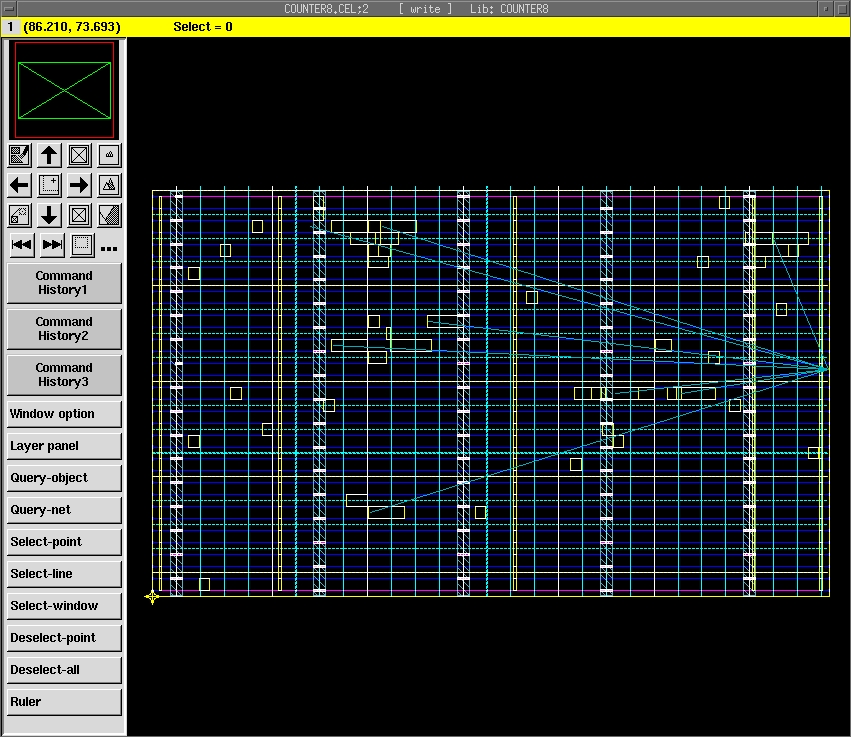

配置されたぞ!

ピン配置の最適化

Clock Tree Synthesis(CTS)

- pre_cts_opt.tcl

- cts.tcl

- show_clk_tree.tcl

- fix_hold.tcl

クロックツリーを生成する.

- まず,astAutoPlace, astSearchRefineにて,配置後の最適化を行う.どれだけ変わったのか,正直分からんけど.

- pdsCROptimizationは,最悪すラックを最小化した後の全てのパスを最適化する,らしい.

- astTranFixは,transition violationを修正する.それ以上のことはわからん.

- astCapFixは,容量違反?(capacitance violation)を修正する.それ以上の事は分からん.

- つぎにcts.tclはついにクロックツリーを張る.

- astClockOptionsにてinverterセル,バッファセルなどをいろいろ指定する.

- astHFCTSはファンアウトが高いネットに付いて,バッファを挿入することにより,スキューや遅延を送らせる効果がある.

- astCTOはClock Tree Optimizationの名の付く通り,最適化だと思う.

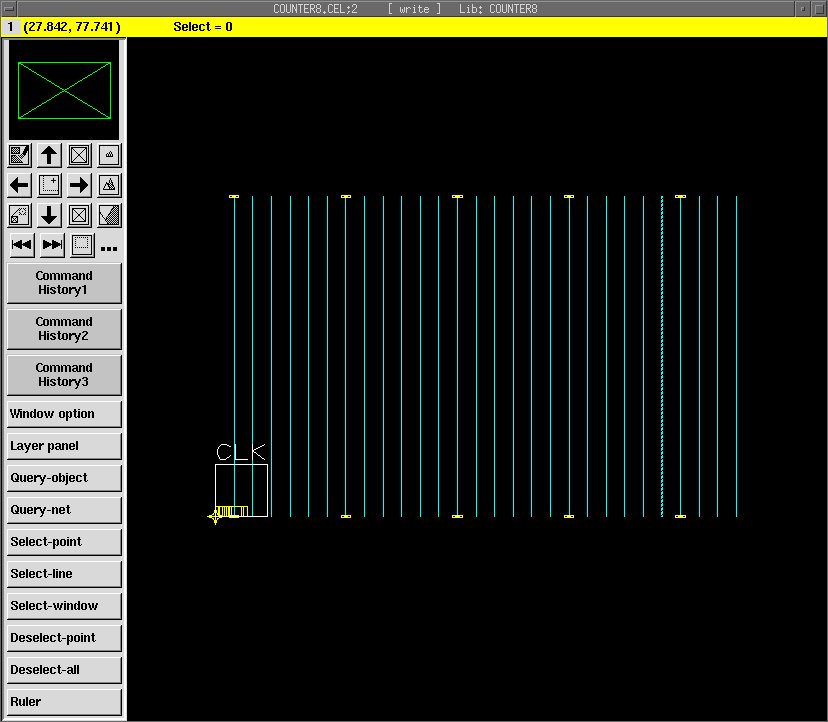

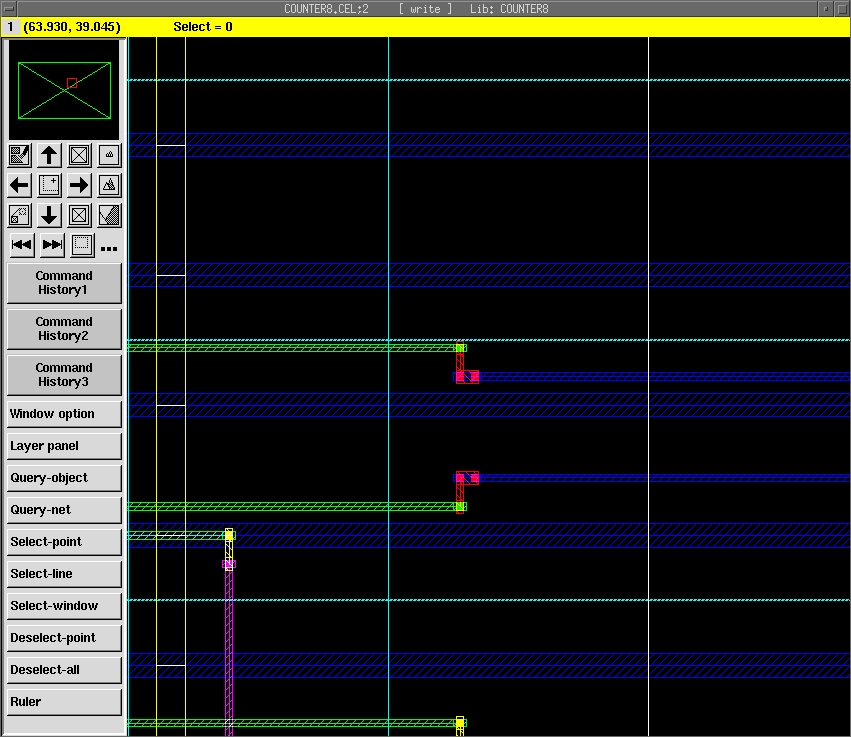

- show_clk_tree.tclで眺めると,こんな感じ.

- astHoldFixにて,ホールド違反を修正する

- astTopoHoldは,トポロジベースのホールド最適化を行う.

- post_cts_timing_setup.tcl

- post_cts_place_opt.tcl

- fix_hold.tcl

CTSのポスト設定をやるのだが,プリ設定と少し違うところがある.比べてみよう.

-- pre atTimingSetupGoto "Model" atCmdSetField delay_model_net_delay_model medium_effort atCmdSetField delay_model_cell_delay_opcond "max min" atCmdSetModels -- post atTimingSetupGoto "Model" atCmdSetField delay_model_net_delay_model medium_effort atCmdSetField delay_model_cell_delay_opcond "max min" atCmdSetModels

これは一緒.

--pre atTimingSetupGoto "Environment" atCmdSetField ignore_interconnect 1 atCmdSetField ignore_propagated_clock 1 atCmdSetField enable_mixed_clock/signal_edges 0 atCmdSetField enable_gated_clock_checks 0 atCmdSetEnvModel --post atCmdSetField ignore_interconnect 0 atCmdSetField ignore_propagated_clock 0 atCmdSetField enable_recovery/removal_arcs 1 atCmdSetField enable_ideal_network_delay 0 atCmdSetField enable_mixed_clock/signal_edges 1 atCmdSetField enable_gated_clock_checks 1 atCmdSetEnvModel

interconnectを無視しなくなる,遅延クロックを無視しなくなる,Gated ClockやMixed Clockをチェックする,など,厳しくなってる気がする.

--pre atTimingSetupGoto "Optimization" atCmdSetField optimization_max_capacitance 0 atCmdSetField optimization_max_transition 0 atCmdSetField optimization_target_setup_slack 0.1 atCmdSetOptModel --post atTimingSetupGoto "Optimization" atCmdSetField optimization_max_transition 0 atCmdSetField optimization_max_capacitance 0 atCmdSetField optimization_target_setup_slack 0.1 atCmdSetField optimization_target_hold_slack 0.1 atCmdSetOptModel

ホールドスラックの記述が加わっている.

- 次の,post_cts_place_optでも,post CTS用の設定にいくつか置き換わっている.

- 実行結果

YUZCUBAの挿入

配線

- まずは,axgSetRouteOptionsを使って,設定をする.このaxgSetRouteOptionsは,複数のコマンドのためのオプションを設定できるのだが,今回はaxgRouteGroupを実行するので,それ用に設定する.

- 次に,配線に用いる最大のレイヤと最小のレイヤを設定する.今回はminがMET2で,maxがMETG2となっている.

- まずはクロックの配線である.axgRouteGroupを行う.このとき,モードをクロック配線にする.”All clock nets”

- クロックが配線された.

- axgSetHPORouteOptionsをもちいて,ハイパフォーマンスルーティングオプションを設定する.

- なぜ普通バージョンとハイパフォーマンスオプションがあるんだろう…

- いよいよ,axgAutoRouteにて配線!!

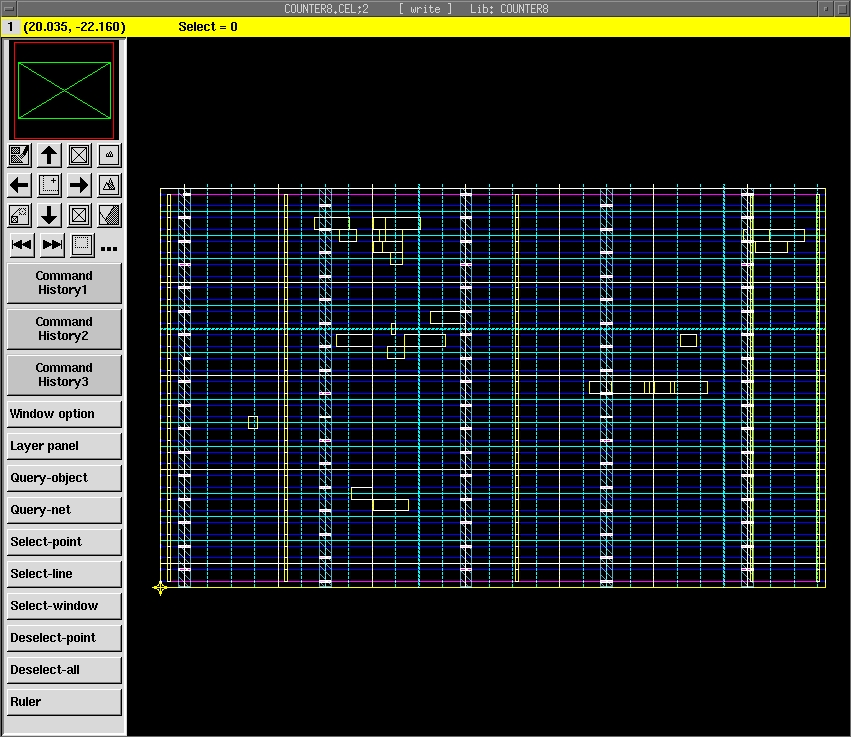

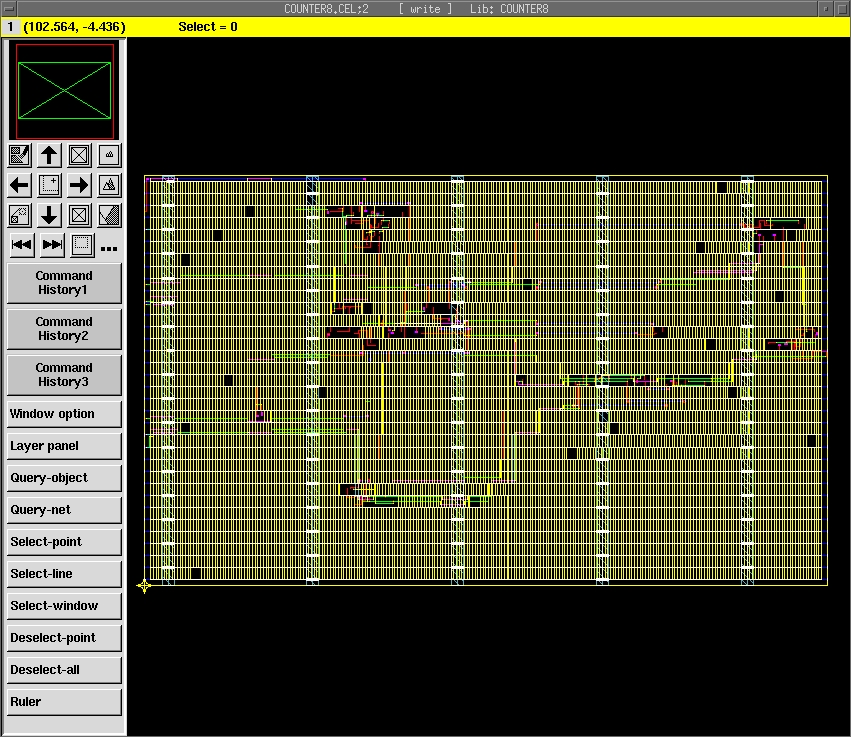

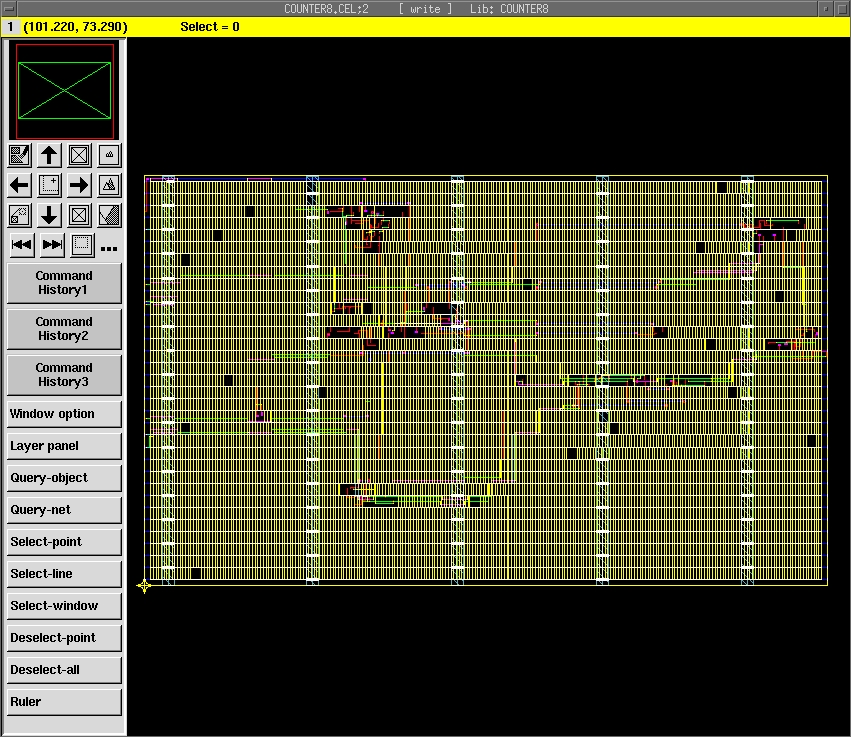

- 配線結果はこんな感じ

ポストルート最適化

- まずは,atTimingSetupで環境を設定する.

- astPostRouteCTOを利用する.マニュアルを読むとGated Clockなどに適しているらしい.クロックスキューを抑え込むときに使う.

- axgTrimClkAntennaを用いて,無用なクロックネットを削除する.これにより,クロックドライバの負荷容量が減る,らしい.

- でも8ビットカウンタごときじゃ全く効果が無かった.

- post_route_optにてポストルート最適化.これは特に複雑な設定をせずに,何回サーチ&リペアすれば良いかを指定しているだけ.

- axgSearchRepairにてサーチ&リペア.30回繰り返す.

- 結果はこんな感じ.あんまり変わってない.

ビアの最適化

- fix_hold.tcl

- via_opt.tcl

- remove_blockage.tcl

- remove_route_guide.tcl

- axgOptimizeContactで,single-cut via?というのを,multicut-viaに変えたり,いろいろ.つまりビアの最適化

- このときに,VIA1_HVからVIA1_HVに名前を変えているが,どういうことでしょう?

- 実行結果.たしかにVIAが2つになってる気がする…けど前どうだったか確認してない.要確認.