誘導結合を用いたチップ間無線接続を利用し、対象アプリケーションに応じてCPU、メモリ、アクセラレータなどのチップを選んで積み重ねることで多様なシステムを構築可能なビルディングブロック型計算システムを研究開発する。あらかじめ仕様が決まっていなくても、チップ積層時に、動的にシステムを最適化する技術を開発する。このための、チップ間無線構築技術、自律構成型ネットワーク、耐故障技術、電力制御回路技術、仮想化と資源管理方式を確立する。開発した手法を用いてプロトタイプビルディングブロック型計算システムを実現し評価する。 本研究では、世界的に突出した技術である誘導結合によるチップ間無線技術をシステム構築の基盤技術とした上で、回路、アーキテクチャ、システムソフトウェアの各階層を統合することで、多様なシステムを目的に応じて自由に構築可能なビルディングブロック型計算システムを実現する設計原理と設計手法を明らかにする。具体的には、次の5つの研究項目を実施する。 (1) ビルディングブロックのための誘導結合によるチップ間無線構築技術の確立。 (2)チップ間無線による自律再構成型ネットワークの方式設計。 (3)ビルディングブロックのための計算システムアーキテクチャの確立。 (4)ビルディングブロックのための電力制御回路技術の確立。 (5)ビルディングブロック型計算システムの仮想化と資源管理方式の確立。 平成25年度にプロトタイプシステムとして、マイクロプロセッサとアクセラレータを数チップ積層したヘテロジーニアスマルチコアシステムを試作し、これを用いて温度特性の測定、電力制御手法の確立、自律型ネットワークの開発、耐故障性プロトコルの開発、ビルディングブロックシステム用OSの開発を行う。平成26年度以降は電力制御回路などに関して小規模な試作を行いつつ、個々の技術を確認する。平成28年度にこれらの成果をまとめてビルディングブロック型計算システムプロトタイプを実装する。平成29年度に、最終的に実装されたシステムをOS、ソフトウェアを含めて評価する。 LSIのプロセスの進展により、小型のチップに多量のロジックが実装できるようになる一方、I/Oピンの不足は深刻な問題であり、開発コストは高騰している。ビルディングブロック型システム技術の確立により、スマートセンサシステムをはじめとする組み込みシステムの実装のコストを大きく減らすと共に、チップの長寿命化、チップの再利用を可能とし、資源の節約に貢献することが期待される。 こちらからダウンロードしてください。

目的

研究の方法

期待される成果と意義

参考資料

Kakenhi-S

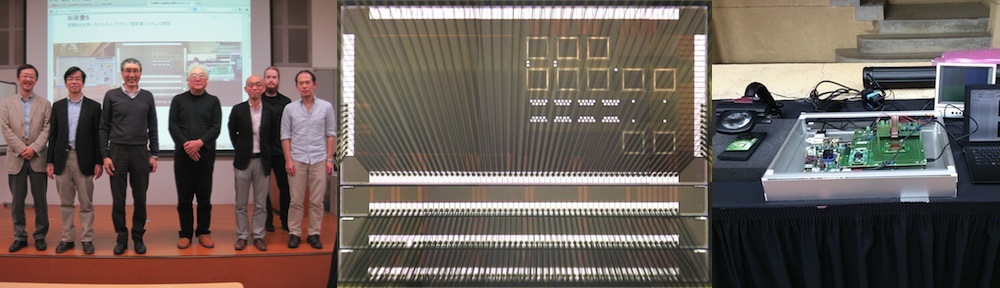

A Study on Building-Block Computing Systems using Inductive Coupling Interconnect