このため、答え(p.180)も変更

このため、答え(p.180)も変更間違いを発見された方は、下の正誤表にないことをご確認の上、こちらまでメールをお願い致し ます。

| ページ | 場所 | 誤 | 正 |

|---|---|---|---|

| p.14 | N1のカルノ-図と回路図 | N1のC1 and not C0のループ | N1は not S and C1 or not C0で良く、簡単化が不十分、回路図もこれに応じて修正 |

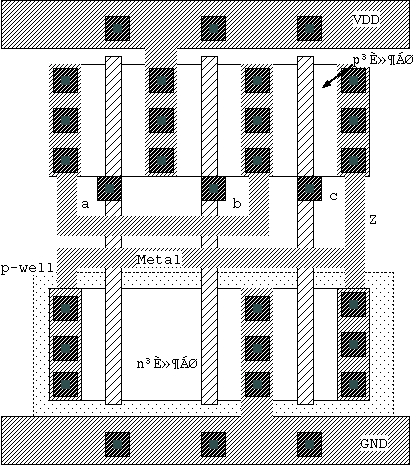

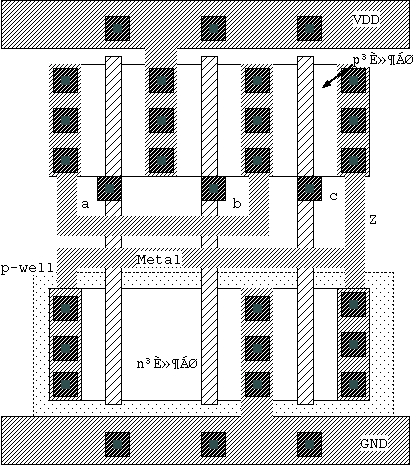

| p.25 | 図2.14 | pMOSとnMOSのサブストレートの矢印の方向 | pMOSが出る方向(右)、nMOSは入る方向(左)に修正 |

| p.30 | 例題2.3 | Bのポリシリコン層がメタル層より上になっている | メタル層の方を上に重ねるように修正 |

| p.56 | (6)の図2.37 | GNDのメタルの場所 |  このため、答え(p.180)も変更

このため、答え(p.180)も変更 |

| p.98 | 図4.11の上半分 | 解説不足と表の位置 | 上の図は74541、1pinはE1, 19pinがE2 2-9pinがD、18-11pinがY、 下の表は上の図に対応 |

| p.98 | 図4.11の下半分 | 解説不足 | 下の図は74245、表が欠けているがG=L,DIR=L,B->Aにデータ転送、 G=L,DIR=H,A->Bに転送、G=Hの時は3ステート状態 対応 |

| p.127 | 図6.2 | セレクタがそのまま出力に行ってしまう | セレクタの出力にバッファを付けた方が解説と合う |

| p.129 | 図6.4 (b) | A0-A16 | A0-A18 |

| p.131 | 図6.5 | CS1のbar, CS2 | CSのbar, OEのbarに変更 |

| p.132 | 解答 | EPROM同様を削除 | ちなみに、CS, OEの場所を入れ替えた場合、TpHL(AC00)*TOE=7*6=13nsec |

| p.138-141 | SDRAM, DDR-SDRAMのタイミング図、例題6.2,6.3およびその解答 | 図が不適切で解説不足です。 | p.138の改訂版 p.139の改訂版 p.140の改訂版 p.141の改訂版 |

| p.180 | 2章{6)の答え | A+BC | AB+C |

| p.183 | 6章{3)aの答え | SDR-SDRAM:バースト長4 21.3MB/sec | 10 clockで4X4B=213MB/sec |

| p.183 | 6章{3)aの答え2 | DDR-SDRAM:バースト長4 30.5MB/sec | 8 Clockで4X4B=266MB/sec |

| p.183 | 6章{3)bの答え | SDR-SDRAM:バースト長8 32.8MB/sec | 14 clockで4X8B=304MB/sec |

| p.183 | 6章{3)bの答え2 | DDR-SDRAM:バースト長8 47.4MB/sec | 10 clockで4X8B=320MB/sec |