回答例 デジタル編 4-10 のみです。

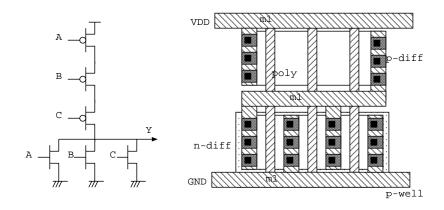

- 4. 論理式  $\overline{A+B+C}$  を実現する CMOS トランジスタの接続図を示せ。

- 5.1 のゲートを実現する場合、下のように n 拡散層 (n-diff)、p 拡散層 (p-diff)、poly が配置されている際に、m1(メタル 1 層)、m2(メタル 2 層) をどのように配置し、どのようにコンタクトを作るかを、分かりやすく示せ。分かりにくい図は減点する。

答

以下に示すのは低電力 CMOS D-FF、74LV74 の規格表の一部である。

6. 3.0V 電源を用いた場合の、L レベル,H レベルに対するノイズマージンをそれぞれ計算せよ。

| $V_{OH}$ | Vdd=3V | 2.8V   | $V_{OL}$ | Vdd=3V | 0.2V   |

|----------|--------|--------|----------|--------|--------|

| $V_{IH}$ | Vdd=3V | 2.0V   | $V_{IL}$ | Vdd=3V | 0.8V   |

| $t_{pd}$ | Vdd=3V | 33nsec | $t_{su}$ | Vdd=3V | 10nsec |

L レベル 0.8-0.2=0.6V H レベル 2.8-2.0=0.8V

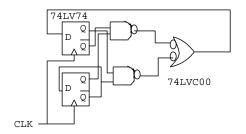

7. 0,1,2,3 の順に数えて 0 に戻る通常の 4 進力ウンタをこの D-FF と 74LVC00  $(t_{pLH}=4.3ns,\,t_{pHL}=4ns)$  で構成せよ。回路図を書け。

8. 上記の回路の最大動作周波数を求めよ。途中経過も示せ。

1/(33+4.3+4+10)=19.4(MHz)

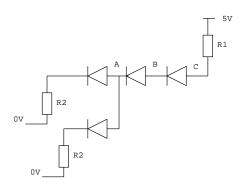

9. 下の回路で A 点、B 点、C 点の電位を求めよ。R1=2K オームとする。

ON 電圧を 0.6V にすると A:2.2V, B:2.8V, C:3.4V

10. アドレスが 18 本、データバスが 8 ビットの SRAM がある。この SRAM の容量はいくらか?一般的に SRAM はどのような用途に用いるか?簡単に説明せよ。

$8*2^{18} = 2^{21} = 2$ Mbit, コンピュータのキャッシュメモリなど、高速で簡単なアクセスが求められる用途