# Parallel Programming Contest2019 HLS Section

A simple CNN: LeNet Get lenet\_fpga from the web site.

### 1. HLS optimization

- Download con19.tar.gz from the website.

- tar cvf con19.tar.gz or archive manager will take care.

- cd con19/lenetcon

- vivado\_hls

- open project -> ./lenetcon/lenetcon

- Place con19 on your home directory.

- Don't change the hierarchy.

# Optimization

- Use techniques in "Vivado\_HLS.pptx".

- Of course, you should check Xilinx's web site.

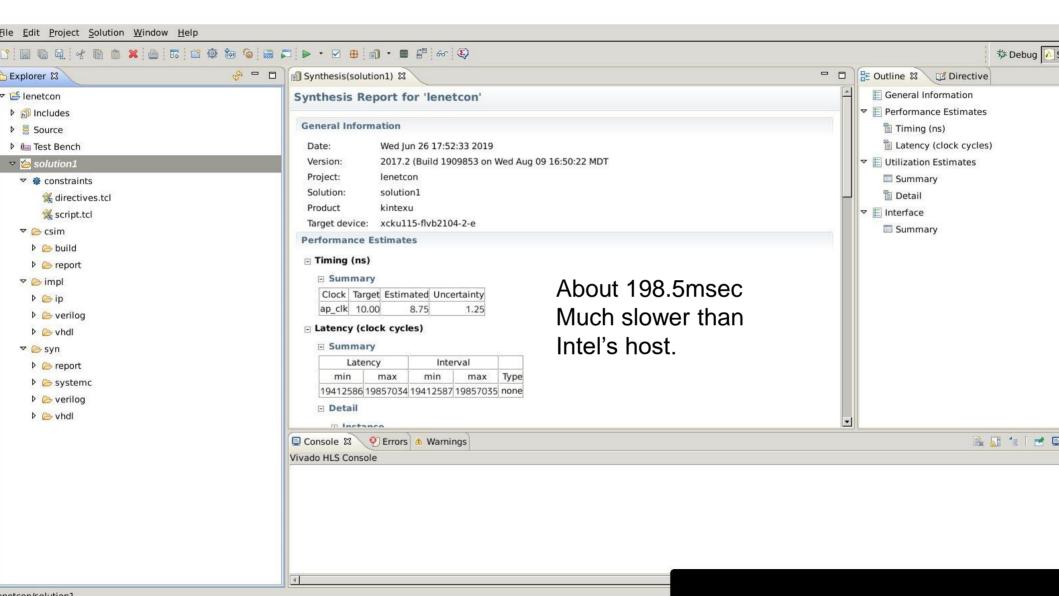

- Synthesize and check the results.

- All resources should be within 60% to avoid long implementation time.

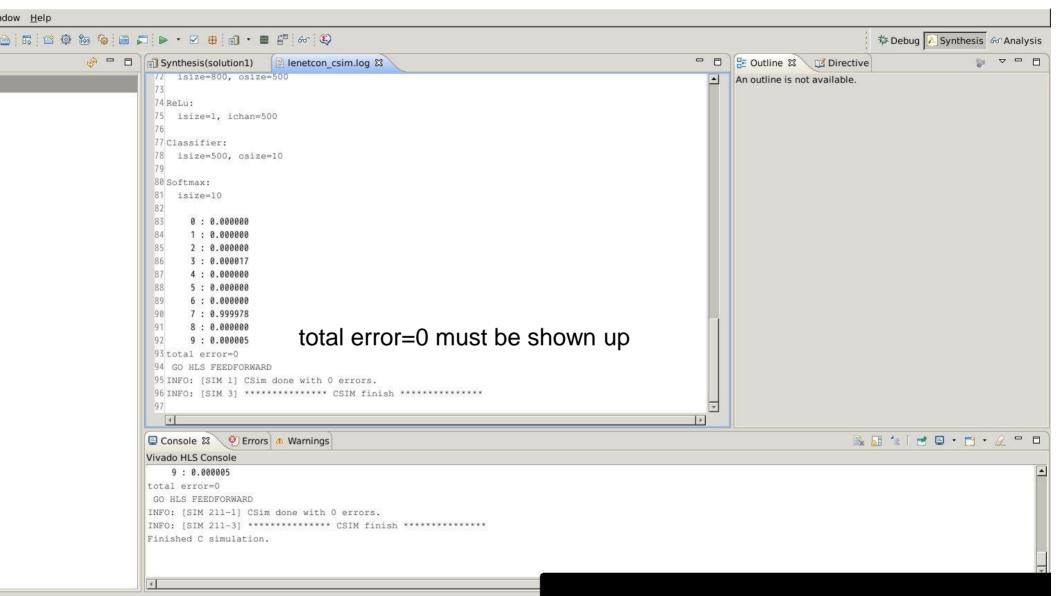

- Make sure your original design must generate the same results.

- After optimization, execute "Export RTL".

- Then exit vivado\_hls.

#### timer

- C simulation does not accept the timer control.

- In lenetcon.c activate

statt[0] = 1; before convl, and

stopt[0] = 1: after fc2

Then, synthesyze.

Now, this problem has been fixed by using #ifdef \_\_SYNTHESIS\_\_

# 2. FPGA design by Vivado

- Arrange "makepro.tcl" for your environment. /home/md401/aa85035/con19-> Your home directory/con19

- /bin/rm –rf tmp\_proj

- Make sure there is no tmp\_proj directory when you apply the script.

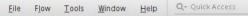

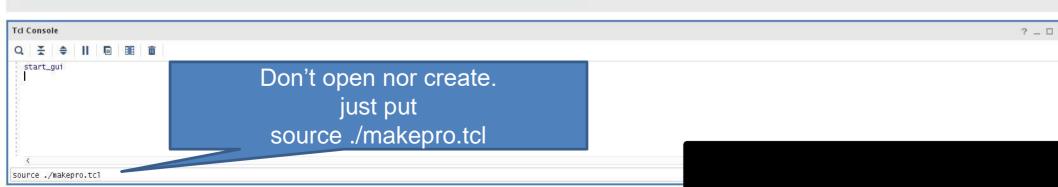

- vivado

- Put "source ./makepro" in the tcl window

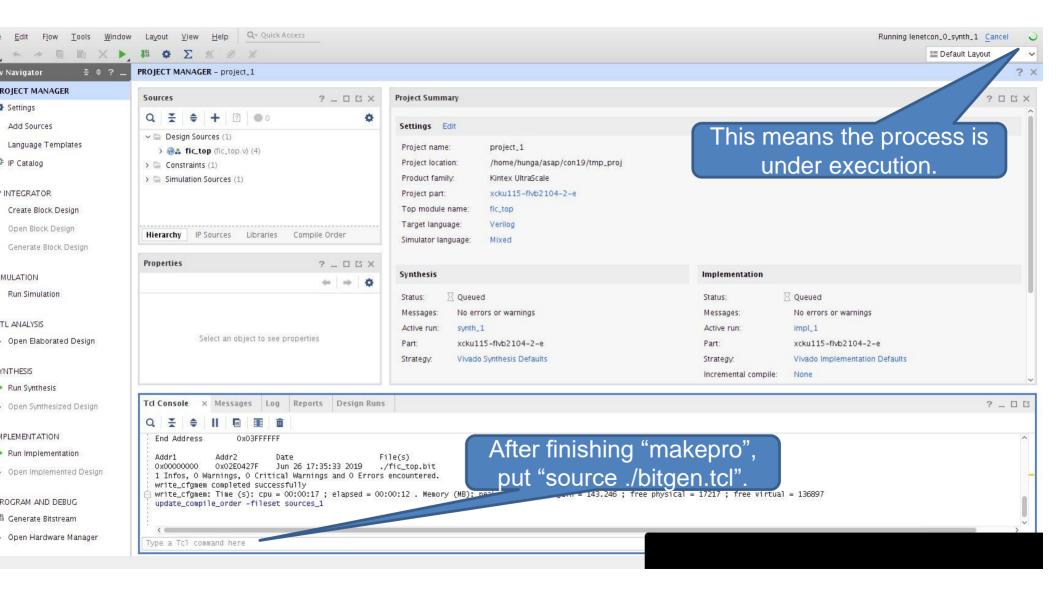

- If there is no problem, all processes will be done automatically.

- It will take about 20 mins. for the base design.

- If your design is big, it sometimes takes a day.

- "Bitstream Generation successfully completed" window will pop up.

- After clicking "Cancel", put "source ./bitgen.tcl".

- fic\_top.bin, the configuration bit is generated.

- File-> Exit

- Caution! vivado/vivado\_hls requires a large disk space.

#### 3. Execute on the FPGA

- You need your account on <a href="mailto:zeus@am.ics.keio.ac.jp">zeus@am.ics.keio.ac.jp</a>

- Send the name if you try to join the FPGA section to yasuaki@am.ics.keio.ac.jp

- ssh –Y <u>zeus@am.ics.keio.ac.jp</u>

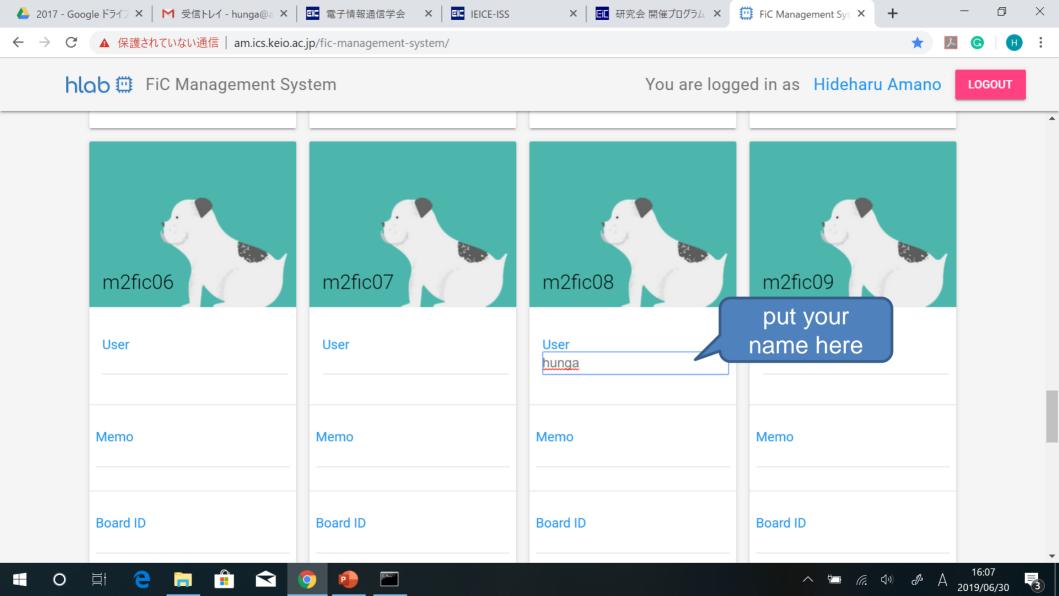

- Start firefox and check the website: <a href="http://www.am.ics.keio.ac.jp/fic-management-system">http://www.am.ics.keio.ac.jp/fic-management-system</a>

- Reserve vacant machine from m2fic08-m2fic11

# Script arrangement

- scp your fic\_top.bin and test.sct.

- Arrange the path for test.sct.

- You must use the absolute path.

- ./test.sh

- The configuration and execution are automatically done.

This must be your fic\_top.bin file

This must be your reserved fic board

#

/home/asap/fic/ras hunga/ficmgr.py -t m2fic08 /p/home/hunga/asap/con19/fic\_top.bin —pm sm1 &

/home/asap/fic/ras\_hunga/ficmgr.py —t m2fic08 —runcmd "/home/hunga/asap/con19/rasbpi/remote" -- runcmdtimeout 5

Read the timer (Ignore the first one)

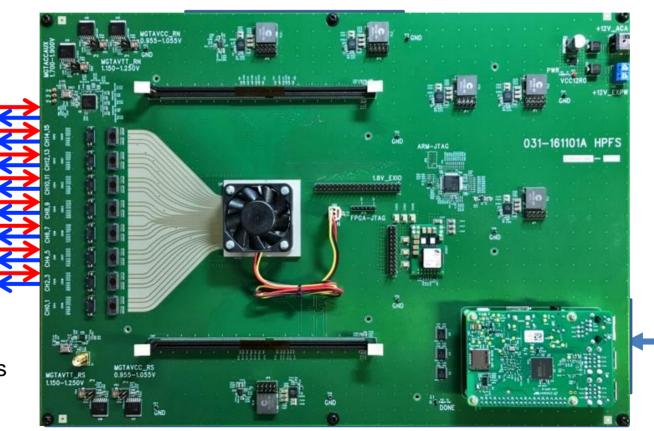

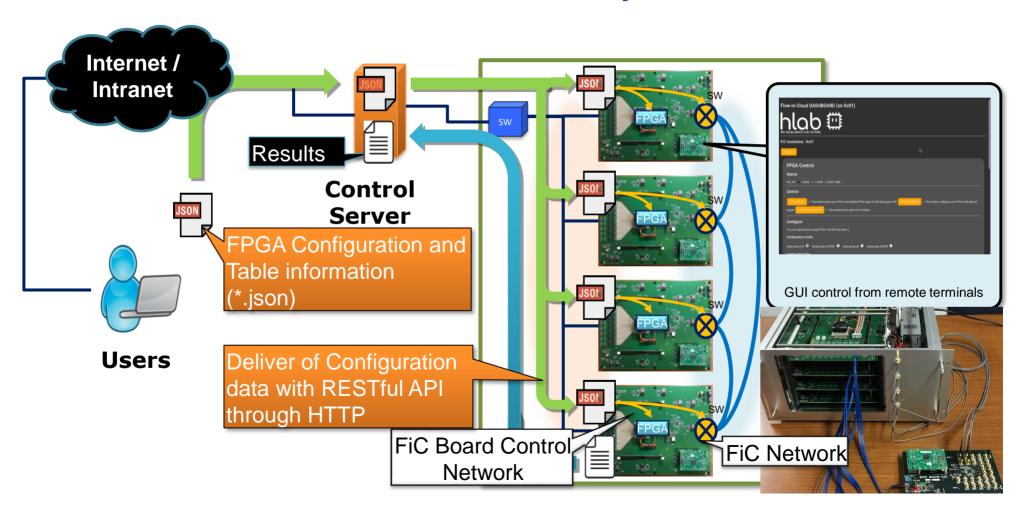

# Flow-in-Cloud (FiC) SW Board

FiC Network 8x4 9.9Gbps

Here, we call each link "channel", and a bundle of 4 channels "bundle".

A board has 8 bundles each of which has 4 channels

Ethernet

Control Network

#### The current FiC system

## Report

- Leave your design in "lenet" directory in your home directory.

- Send the mail to <a href="https://hunga4125@gmail.com">hunga4125@gmail.com</a> with a report and your account number.

- The result must be the same as the current version.

- The deadline is 8/2 24:00. Never delayed.

- The ranking will appear on the web site.

- If you have any question, mail to <u>yasuaki@am.ics.keio.ac.jp.</u>