## 第1

## はじめに

## 1.1 なぜコンピュータアーキテクチャを勉強するのか?

コンピュータアーキテクチャの勉強とは、簡単に言うと、コンピュータの中身を知り、それがどのように動いてどのように作られているかを理解することだ。アーキテクチャというのは「建築」という意味で、コンピュータアーキテクチャはコンピュータという建築物を、どのように作っていくかについての方法論である。

Web を作ったり、グラフィックを作ったりするのは格好いいので、コンピュータのプログラムはするかもしれないけれど、コンピュータを設計するわけではないので、コンピュータの中身には興味がない。

ケータイは便利だし、ゲーム機は凄い。iPod は格好いいし、地デジはきれい、こういう製品を作る所に行きたいけど、コンピュータは関係ない。大体マイクロプロセッサは、もう日本では作ってないし、Intelが作るのを買えばいい。コンピュータの構成なんて、もう進歩が止まっている分野で大きな発明や面白いことは何もない。要するに、コンピュータアーキテクチャは興味も関心もない。多くの電気、電子情報系の大学では、基礎科目としてコンピュータアーキテクチャ、コンピュータ工学などが設けられている。進級のために履修はするけど面倒なだけ、と思っている方々もおられるかと思う。しかし、これは誤った考え方である。

まず第一に、コンピュータのプログラマは、それが何を対象にするのであれ、一通りのコンピュータアーキテクチャの知識を持っている必要がある。コンピュータアーキテクチャはプログラマのために、抽象化を行って、細かい所は気にしなくてもプログラム書けるようにしている。したがって、プログラマを目指す方々は、コンピュータハードウェアの詳細を知る必要はない。しかし、コンピュータアーキテクチャに関して一応の知識がないと、良いプログラムは書けないし、もちろんプロにはなれない。

次にIT機器の開発者を目指す人たちは、より詳しくコンピュータアーキテクチャに関して知っておく必要がある。ケータイ、ゲーム、情報家電、自動車に至るまで、あらゆるIT機器にコンピュータは組み込まれている。これらは組み込みコンピュー

2

タと呼ばれて、多くの場合、その IT 機器を制御する中心としての役割を果たす。現在、日本の半導体業界は、組み込みコンピュータをその部品の一部とし、他にメモリ、専用プロセッサ、インタフェースなどを一つのチップに入れるシステム LSI あるいは SoC(System-on-a Chip) を主力製品としている。ケータイに入っているチップはこのシステム LSI の代表であり、最近はどの IT 機器もこれが頭脳としての役割を果たす。したがって、IT 機器に関連する場合、コンピュータアーキテクチャを理解していないと、製品開発をすることができないし、もちろんマネージャになることも、下手をすると営業をするにも支障が出る。

このように、今やコンピュータは、デスクトップPC,ラップトップPCあるいはサーバなどだけではなく、IT 産業の基礎となるパーツであり、IT 産業に携わる者の基礎的な知識として必要である。これが多くの大学の電気、電子、情報系の基礎科目にコンピュータアーキテクチャが入っている理由である。

また、コンピュータアーキテクチャは、進歩が止まってしまった分野でも、重要性が小さくなっていく分野でもない。確かにコンピュータの中心部、CPU(Central Processing Unit:中央処理装置)の構成自体は、ほぼ固まっているし、その動作周波数もこれ以上高くできなくなっている。しかし、このことによって新しいアーキテクチャの研究開発はむしろ活気付いている。多数の CPU を使ったマルチコア、メニーコア、限られた処理のみを高速化するアクセラレータ、汎用化されたグラフィックプロセッサ GP-GPU(General Perpuse Graphic Processing Unit)、柔かいハードウェアと呼ばれるリコンフィギャラブルシステム、動的に構成を変更する動的リコンフィギャラブルプロセッサなど新しいアーキテクチャが次々に登場しており、実際の製品にも使われている。

つい最近まで、コンピュータの性能は圧倒的に半導体のプロセスによって支配された。アーキテクチャが同じでも、新しい半導体プロセスを使えば、性能は上がり、コストと消費電力は下がった。このため、アーキテクチャなんてどうでもいいから新しいプロセスで新しい製品を作れば、うまく行ったのである。しかし、最近、半導体の微細化加工技術が限界に近づくにつれ、新しいプロセスの開発は難しくなり、プロセスの代替わりの間隔は開きつつある。また、プロセスが新しくなっても、特に性能面では目立って改善されないようになった。一つのプロセスが長い時間使われる場合に重要になるのは、それをいかに活用するか、すなわちコンピュータを含めた広い意味でのアーキテクチャである。今後IT製品においては、半導体プロセスを新しくするよりも、より良いアーキテクチャを使う方が良い製品につながっていく。すなわちアーキテクチャの重要性は今後どんどん大きくなっていくのである。

今まで、コンピュータアーキテクチャを学ぶことの実利についてを紹介したが、コンピュータアーキテクチャを学ぶもっとも正しい動機は、それが面白いからだ。解説が進むに従って、原理的には非常に簡単なものが、(もちろんソフトウェアの力が大きいとはいえ)、凄いことをやってのけることがご理解いただけると思う。本書を完全にマスターすれば、自分自身でコンピュータを設計し、FPGA(Field Programmable Gate Array) や実際のチップ上で動かすことができるのだ。また、建築物同様、良くで

きたコンピュータは美しい。互換性を守りながら性能を上げるために、理解不能なレベルで複雑化した Intel 系の CPU にすら、長年、増築と改築を重ねた歴史的建造物のような美を感じることができるかもしれない。

## 1.2 コンピュータの基本

コンピュータは大きく分けて三つの領域で主に使われる。

- デスクトップ PC、ラップトップ PC: いわゆるコンピュータっぽいコンピュータ。 Windows, Linux が Operating System として走り、Intel 系の命令が走る CPU(中央処理装置) を用いている。無線や LAN でネットワークに接続して用いる。最も発展が急速で、性能と値段が重要。

- サーバ: 大企業や大学のシステムを統括する大型システム。ネットワークを介してデスクトップ PC やラップトップ PC と接続し、ファイルを管理し、デスクトップなどで手に余る大規模な計算を行う。あるいは、トランザクション処理と言って、データベースに接続されて、データ管理を行う。銀行の ATM、航空券の予約システムはこの例である。Web を管理して、検索等を行う Web サーバも大規模なサーバの一つ。故障しないで長期間動くこと、故障からの回復が早いこと等信頼性 (dependability) が重要。

- 組み込みシステム: 様々な IT 機器のなかに組み込まれており、外からは見えないし、普通はプログラムもしない。洗濯機やクーラーを制御するのは 8bit のコンピュータで可能だが、PS3 などのゲーム機には、Cell という超強力なプロセッサが組み込まれているし、ケータイの CPU も特定用途には強力である。コストと消費電力と、特定分野に限った性能が重要。

## 1.2.1 コンピュータの基本形

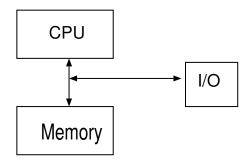

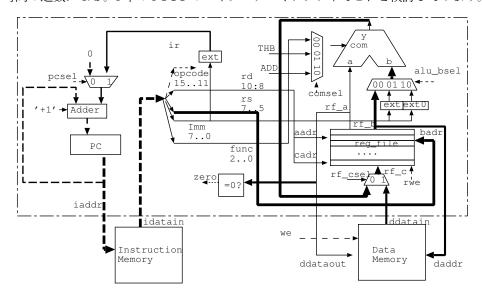

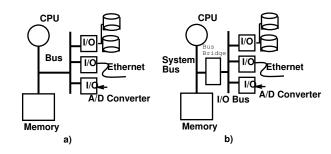

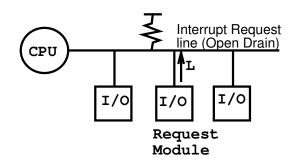

コンピュータはそれがデスクトップ PC であれ、組み込み用であれ、基本的に図 1.1 に示すように、CPU(Central Processing Unit:中央処理装置) と命令やデータを記憶しておくメモリ、外部とのやり取りを行う入出力 (I/O) の三つの部分から出来ている。CPUは、メモリから命令を基本的には順番に取ってきて、その中に書いてあることを実行することを繰り返す。これをプログラム格納型 (Stored Programming) と呼ぶ。データは入出力装置から取り込み、メモリ上に置き、CPU はこれを読み書きしながら処理を進め、結果をメモリから出力装置に出力して表示する。

4 第1章 はじめに

図 1.1: コンピュータの三つの要素

## 1.2.2 コンピュータの歴史と発展

最初のコンピュータは何で、誰が発明者なのか?という問題は、なかなか難しく、これを検討するだけで一冊の本ができてしまう<sup>1</sup>のだが、最初の電子計算機として最も良く知られているのは、ペンシルバニア大学の ENIAC(1946年)である。ENIACは、全ての回路を真空管で実装した(18000本)点で電子計算機であったが、プログラミングにはスイッチの設定やケーブルの結線を人手で変更する必要があった。この ENIAC の経験を基に、命令をメモリ上に格納し、これを順に取ってきて実行するプログラム格納方式の考え方が生まれ、ケンブリッジ大学の EDSAC(1949年)が誕生した。これがはじめてのプログラム格納型計算機であり、現在のコンピュータは基本的にこの方式から変わっていない。

コンピュータの歴史についても様々な文献や著書があり、ここでは詳しく触れないが、コンピュータについて歴史上最も重要な変革があったのは実はつい最近である。 すなわち、コンピュータの歴史は、その使われ方から以下のように分けられる。

## 1.2.3 計算機登場~1980年後半: 中央集権時代

メインフレームと呼ばれる大型計算機が計算センターにどんと置かれており、これを共同で利用した。初期は、一人の利用者がコンピュータを占有したが、その後オペレーティングシステムが複数のジョブを管理することができるようになり、あらかじめパンチカードから入力したプログラムをテープやディスクに入れておき、順に実行するバッチ処理が可能になった。さらに端末をつないで対話的にジョブを実行する TSS(Time Sharing System) が登場した。この時代、計算機といえばメインフレーム=IBM マシンであった。このメインフレームは、ハードウェアの素子技術によって以

$<sup>^1</sup>$ この問題に興味のある方は、星野力著「誰がどうやってコンピュータを創ったのか?」(共立出版) をお勧めする。

下のように世代 (generation) 分けされる<sup>2</sup>

- 第1世代: 真空管 (1946~1950 年代中ごろ)

- 第2世代: トランジスタ (1950年代中ごろ~1960年代中ごろ)

- 第3世代:集積回路(1960年代中ごろ~)

IBM は、1964年に IBM360を発表し、これがメインフレームのアーキテクチャの方向を決定づけた。キャッシュ、割り込み、仮想記憶、本格的オペレーティングシステム (OS)、リアルタイムシステムやトランザクション処理等、現在の計算機の技術のほとんどはメインフレームによって発達を遂げた。一方で、用途に応じたコンピュータ自体の分化も進んだ。DEC 社の PDP-11を代表するミニコンピュータは、メインフレームに比べて安価で気軽に使えるため、研究・教育施設に広く用いられた。また、科学技術計算を専用に行うユーザのためには、強力な数値演算能力を持つ CRAY-Iに代表されるスーパコンピュータが登場した。

## 1.2.4 1980 年代後半~2003 年:マイクロプロセッサ大成長時代

一人が一台の PC(Personal Computer) あるいは WS(Work Station) と呼ばれるコンピュータを持ち、これらがネットワークで接続されていて、互いに情報を交換しながら処理を行なう、現在一般的になっている使い方が確立したのがこの時代である。

初めてのマイクロプロセッサと呼ばれる Intel の i4004 が誕生したのは、1971 年である。マイクロプロセッサは、計算機の CPU を 1(数) チップに格納したもので、電子機器制御、ゲーム、簡単なコンピュータに用いられ、8bit, 16bit, 32bit と bit 数を増やしながら急速に発達を遂げた。さらに、1980 年代前半に普及した RISC(Reduced Instruction Set Computer) 方式により、マイクロプロセッサの性能は年々飛躍的に増大(年間 1.5 倍)するようになった。

ここに以下の状況が加わった結果、1980年代後半に革命的な事態が起こった。

- ビットマップディスプレイによるウインドウ、マウス等 WS/PC のユーザインタフェース技術が確立した。

- 高級言語(C言語)の普及により、アセンブラに依らずにシステムが全て記述できるようになった。

- UNIX, MS-DOS などの汎用 OS が普及し、OS の移植が容易になった。

<sup>&</sup>lt;sup>2</sup>第3世代後に大規模集積回路 (LSI) で構成された第4世代を設定する考え方もあるが、LSI は集積回路 の単に大きいものに過ぎないので、どこで切るかが苦しくなっている。日本で 1982 年から 10 年間に渡って行なわれた第5世代コンピュータプロジェクトが失敗したため、これ以降、第5世代という言葉を使う人は居なくなり、計算機を世代で分ける考え方は消滅した。

第1章 はじめに

• ローカルコンピュータネットワークが、Ethernet によって標準化され、さらに、インターネットの登場により、グローバルネットワークの基盤技術が整った。

これらの技術的基盤が整備されることによって、それまで広くもちいられてきたメインフレームに代わって、最新の半導体技術を用いた高性能マイクロプロセッサを用いた、個人用のPCやWSが急速に普及した。これらのPC/WSは、Windows, Linuxの汎用OSを搭載し、ネットワークに接続して用いる。この結果、コンピュータの主流はメインフレームからPCやWSに移り、またPCとWSの区別は消滅した。さらには、ラップトップ型の可搬型のコンピュータ、携帯端末が普及した。

## 1.2.5 2004年~:マルチコア時代

6

2003年まで、マイクロプロセッサの動作周波数は年々向上し、性能も年間 1.5 倍の伸び率を示した。しかし、以下の原因で、マイクロプロセッサ CPU 単体の性能は壁にぶつかった。

- 高い周波数を用いたことにより発熱が増大し、これ以上周波数を上げると放熱 することが困難になった。

- CPU の動作速度にメモリが付いていけなくなり、これ以上動作周波数を上げて も性能があまり上がらなくなった。

- 単体 CPU の性能向上を支えてきた、命令レベルの並列処理が限界に達した。

このため、CPU 単体の性能を上げるよりも複数の CPU を 1 チップに搭載した構成が一般的に使われるようになった。2010 年現在、高性能のデスクトップでは 1 チップに 4 つの CPU を搭載する構成が一般化している。また、100 を越える数の CPU を搭載するメニーコアも作られ始めている。

## 1.3 本書の目的

従来、コンピュータアーキテクチャのテキストは、コンピュータの専門家を対象とした分 Patterson&Hennesy のテキスト [1] および Hennessy&Patterson [2] の厚い決定版テキストを除いては、コンピュータのプログラマやユーザーが、自分達の利用しているコンピュータの構造を「知識」として理解するために書かれたものが多かった。このようなテキストは、おおむねトップダウンに書かれており、コンピュータアーキテクチャの様々な技術を概観し、知識として理解するためには優れたものが数多く書かれている。

しかし、システム LSI 時代にコンピュータのアーキテクチャを学ぶ場合、その構造と動作を概観するのではなく、具体的に構造を理解し、できれば簡単なプロセッサを、

1.3. 本書の目的 7

自分で設計した経験を持つことが望ましい。本書は、このような時代の要求に基づき、コンピュータアーキテクチャの初学者を対象として、最終的にはパイプライン化された RISC を目標として、ボトムアップに設計しながら、設計演習とプログラミング演習を通じてコンピュータアーキテクチャの実際的な設計技術を修得するのが目的である。設計には、Verilog-HDL を用い、シミュレーションにはフリーソフトで誰でも使える Ikarus Verilog と、gtkwave を利用している。PC をお持ちの方ならば自宅で誰でも実際に設計演習が可能である。また、web 上の教材を用いれば、実際の FPGAのキット上で実習が可能である。<sup>3</sup>

本書の初版が出版されたのは2001年である。今回改訂したのは、以下の点である。

- 初版本では、PARTHENON/SFL を用いた。これは、当時フリーソフトで利用できた唯一のハードウェア記述言語とそれに基づく設計環境であったこと、美しい言語構造で教育用途に優れていた点である。今でも SFL が Verilog-HDL よりも優れたハードウェア言語であるという考えには変わりがない。しかし、SFL を実際の設計現場で利用する機会がほとんどなくなったこと、Verilog-HDL にもフリーソフトで優れたシミュレーション環境が普及したことから改訂に踏み切った。本書の Verilog 記述に対応する SFL 記述は web 上で公開するので、PARTHENONの利用者はご面倒だがそちらを参照していただきたい。

- 初版本では、教育用マイクロプロセッサ PICO を用いた。PICO は、本格的な RISC の骨格を持ちつつ、分かりやすい、ということを目的に設計したプロセッサであった。ところが、「これでもまだ難しい」という批判があり、より分かり やすい POCO に移行した。PICO についての解説、SFL 記述も web 上で公開する予定である。

- 本書はコンピュータアーキテクチャの入門書ではあるが、それでもこの 10 年間 にコンピュータは進歩を続けた。この内容を取り込む必要があった。

本書は、プログラミング言語 (特に C 言語) に関する初歩的な知識とブール代数や順序回路設計等、論理設計に関する初歩的な知識を前提としているが、これらは電気情報系の大学あるいは高専の初年度に学習するごく簡単なレベルである。すなわち、本書は大学以上、高専上級生レベルの、コンピュータアーキテクチャの初学者を対象としている。しかし、これらの知識が全くない初学者も各章の例題や演習を実際に実行しながら自習すれば、充分内容が理解できると思う。

$<sup>^3</sup>$ 私自身翻訳に携わった [3] は本書と全く同じ目的意識に基づいた良書である。しかし、本書の初版本が出版されたのは 2001 年で、[3] よりもずっと以前であり、本書がこれに影響されて書かれたわけではない。また、コンピュータアーキテクチャのテキストについてのサーベイは web を参照されたい。

## 第2

# データパス: コンピュータで演算をする所

## 2.1 数の表現

まずはコンピュータ内の数の表現を復習しておこう。ご存じのとおり、ディジタルシステムでは数を  $1 \ge 0$  の 2 進数で表現する。これは  $1 \ge 0$  が H レベルと L レベルの二つのレベルで処理を行うディジタルシステムと本質的に良く適合するためである。基本となるのは符号なし数、すなわちただの 2 進数である。一番右の桁が 1 の位であり、これを LSB(Least Significant Bit) という。一番左が  $2^n$  の位であり、これを MSB(Most Significant Bit) という。

コンピュータでは長いビット数を扱うことが多いため、通常の2進表現では見にくいことがある。このような場合は、4 桁ずつ区切って、16 進数として表現する。この時、10 進数との混乱を避けるため、C 言語の書き方にならって頭に 0x を付けて表す場合が多い。ちなみに、かつては8 進数や BCD(Binary Coded Decimal: 2 進化 10 進数) も用いられていたが、現在はほとんど使われないため省略する。

| 10 進 | 2進   | 16 進 | 10 進 | 2 進  | 16進 |  |

|------|------|------|------|------|-----|--|

| 0    | 0000 | 0    | 8    | 1000 | 8   |  |

| 1    | 0001 | 1    | 9    | 1000 | 9   |  |

| 2    | 0010 | 2    | 10   | 1000 | A   |  |

| 3    | 0011 | 3    | 11   | 1000 | В   |  |

| 4    | 0100 | 4    | 12   | 1000 | C   |  |

| 5    | 0101 | 5    | 13   | 1000 | D   |  |

| 6    | 0110 | 6    | 14   | 1000 | E   |  |

| 7    | 0111 | 7    | 15   | 1000 | F   |  |

|      |      | !    |      |      |     |  |

上記を符号無し数 (unsigned) と呼ぶ。ではマイナスの数を表現するためにはどのようにすれば良いだろうか? 単純なアイディアは符号ビット s と符号無し数 (絶対値) を

組み合わせることで、s=1 で 1001 ならば-9、s=0 で 1001 ならば9とする方法である。 これは可能だが一般的ではない。

マイナスの数を表現するのに普通に使われる方法は、2の補数表現である。この方法には以下のメリットがある。(1)一番上の桁で符号がすぐに判定できる。(2)マイナスの数を加算することで減算ができる。(3)+0と-0が生じない。(符号ビットと符号無し数の組み合わせだと+0,-0ができてしまう)。このため、現在すべてのコンピュータで用いられている。

2の補数とは、足した結果、すべての桁が0になり、桁上げが生じる数のことである。具体的には、(1) ある数の1 と0 をひっくりかえす。(2) 1 を足す。で、求めることができる。例えば、4 桁の数があるとするならば、下に示すように、-8 から7 まで16 個の数を表すことができる。

| 2進   | 2 の補数 | 符号なし数 | 2進   | 2 の補数 | 符号なし数 |   |

|------|-------|-------|------|-------|-------|---|

| 0000 | 0     | 0     | 1000 | -8    | 8     |   |

| 0001 | 1     | 1     | 1001 | -7    | 9     |   |

| 0010 | 2     | 2     | 1010 | -6    | 10    |   |

| 0011 | 3     | 3     | 1011 | -5    | 11    |   |

| 0100 | 4     | 4     | 1100 | -4    | 12    |   |

| 0101 | 5     | 5     | 1101 | -3    | 13    |   |

| 0110 | 6     | 6     | 1110 | -2    | 14    |   |

| 0111 | 7     | 7     | 1111 | -1    | 15    |   |

|      |       | '     |      |       |       | ) |

上の表も見てもわかるように、2の補数を用いると一番上の桁が1ならば、それはマイナスの数になる。つまり、2の補数表現では、MSBを符号ビットと呼ぶ。

2 の補数表現で m 桁の数の桁数を増やす必要が生じた場合は、MSB が 0 ならば 0 を、1 ならば 1 を補う。例えば、4 桁の'6'=0110 を 8 桁で表す場合、上に 0 を 4 つ 補い 00000110 とする。しかし、'-6'=1010 を 8 桁で表す場合に同じことをすると、00001010=10 になってしまう。1 を 4 つ補い 11111010 とすれば、8 桁にしてもちゃんと-6 になる。このように桁数を増やす方法を符号拡張 (sign extension) と呼ぶ。符号拡張は後に命令コード中に頻繁に表れて、皆さんを悩ますことになる。

## 例題 2.1

下の bit 列を 16bit に符号拡張し、2 進数で示せ。

- 1. 0011

- 2. 10010010

- 3. 0x93

#### 答

1. 0011: 頭に0を付けて000000000000011

2.1. 数の表現 11

- 2. 10010010: 符号拡張して 11111111110010010

- 3. 0xa3: 10100011 なので符号拡張して 11111111110100011

## 例題 2.2

8bit の符号付き数で、(1)-12,(2)-122 を示せ。

## 答

- 1. 12 は 8 ビットの 2 進数で 00001100 となる。1 の補数は 11110011 であり、これ に 1 を足して 11110100 となる。

- 2. 122 は 8 ビットの 2 進数を求めることがまず面倒であるが、2 で割った余りを順に下の桁から並べて行けば良い。122/2=61..0,61/2=30...1,30/2=15...0,15/2=7...1,7/2=3...1,3/2=1...1 となるので、01111010 である。後は同様に 1000101+1=10000110 となる。

1より小さい桁が必要な場合、固定小数点 (Fixed Point) 数が用いられる場合がある。 この方法では小数点の場所をあらかじめ決めておくだけで、数字自体の記述は、通常 の数の表現と同じである。

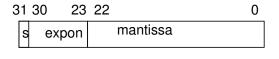

より桁数の大きな科学技術計算には浮動小数点 (Floating Point) 数が用いられる。現在、IEEEにより標準化されており、32 ビットの単精度、64 ビットの倍精度が存在する。図 2.1 に示すように、それぞれ仮数部と指数部を持っており、(仮数部) × (2の指数部乗)で数を表す。これ自体は簡単だが、浮動小数演算でいつも問題となるのは、仮数部に入らなくなった桁を省略して、指数部に繰り込む際に生じる「丸め」の処理である。この処理は繁雑で、ハードウェアを実装する際に常に悩ましい問題となる。

図 2.1: 浮動小数

さらに、コンピュータで扱う2進ビット列は、数を表すだけとは限らない。文字コードなど、数以外のデータを表す場合も多い。文字コードとしては英数字を表すコード

として 8bit の ASCII コードが、より多くの文字を表すのには 16bit の Unicode が一般 的だが、他にも多種多様なコードが使われる。

さて、ここで覚えておいて欲しい重要な概念がある。コンピュータで扱うデータは、それ自体は意味を持っていない。1/0 の列によって表されたデータは、命令なのか、符号無し数なのか、符号付き数なのか、区別を持っていない。それがどんな意味を持つかは、扱う側、つまりコンピュータのハードウェアやプログラマの解釈次第なのである<sup>1</sup>。

## 演習 2-1

下の bit 列を 16bit に符号拡張し、2 進数で示せ。またこれを符号無し数と考えて 16 進数で表記するとどのようになるかを示せ。

- 1. 11000110

- 2. 0x3D

- 3. 0x80

## 演習 2.2

8bit の符号付き数で、(1)-17,(2)-115 を示せ。

## 2.2 ALU(Arithmetic Logical Unit)

さて、コンピュータの中で行う演算とはどのようなものだろう。まず加減乗除の四則演算が思い浮かぶだろう。その他代表的な演算は以下の通りである。例では A=10110110 と B=11100010 を入力とする。

- 論理演算: 各桁の論理演算を行う。

- 論理積 (AND): A,B 各桁の論理積を出力する。例では A AND B = 10100010 となる。

- 論理和 (OR): A,B 各桁の論理和を出力する。例では A OR B = 11110110 となる。

- 排他的論理和 (XOR): A,B 各桁の排他的論理和を出力する。排他的論理和とは 0 XOR 0 = 0,0 XOR 1 = 1,1 XOR 0=1,1 XOR 1 = 0、すなわちビットが異なっていれば 1 となる。例では A XOR B = 01010100 となる。

<sup>&</sup>lt;sup>1</sup>これが原因で、処理の信頼性が低くなると考えた一部の研究者は、データに意味を付与するタグ付き アーキテクチャというのを考えたが、苦労した割にメリットが少ないため、今の所、成功していない。

- 反転 (NOT): A 各桁の反転を出力する。例では 01001001 となる。

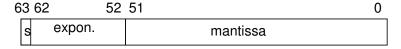

- n ビットシフト: 各桁を n 桁分ずらして (シフトして) 出力する。

- 左シフト (Shift Left:SL): 左方向にずらす。n 桁シフトすると 2<sup>n</sup> 倍したこと になる。空いた最下位 (最も右) の桁には 0 を詰める。1bit シフトの場合、01101100 となる。

- 右シフト (Shift Right:SR): 右方向にずらす。n 桁シフトすると  $1/2^n$  倍したことになる。ここで右シフトには 2 種類ある。

- \* 論理シフト (SRL: Shift Right Logical): 空いた最上位 (最も左) の桁に は 0 を詰める。例では 1bit シフトの場合、01011011 となる。

- \* 算術シフト (SRA:Shift Right Arithmetic): 空いた最上位 (最も左) の桁 に符号ビットを詰める。つまり符号を保持したままシフトする。例では 1bit シフトの場合、11011011 となる。

上記の例を図 2.2 に示す2。

図 2.2: シフト操作

#### 演習 2.3

8bit データについて A=10100110, B=01100100 とする。以下の演算の結果を求めよ。

- 1. A AND B

- 2. A OR B

- 3. A XOR B

- 4. SL A (1bit)

- 5. SRA A (1bit)

- 6. SRA B (1bit)

<sup>&</sup>lt;sup>2</sup>SLA Shift Left Arithmetic も定義可能だが、あまり一般的ではない

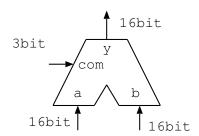

コンピュータでは、上記の演算を行う装置を一まとめにして扱う。これを、ALU(Arithmetic Logic Unit) と呼ぶ。乗算と除算は、やや複雑で1クロックで終わらせるとが難しいため、基本的な ALU の中には入れない場合が多い。

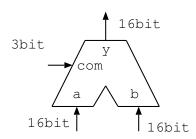

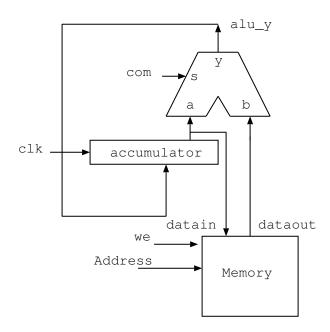

ALU は図 2.3 に示すように a, b 二つのデータ入力とコマンド入力 s、出力として y を持っている。コマンド入力 s の内容に応じて、a,b の入力に対して所定の演算を行って、y に出力するのが ALU の役目である。

図 2.3: ALU のモデル

ある ALU で 8 つの演算が可能な場合、3 ビットの com の値によってその内容を切り替える。例えばここでは以下のように決めよう。

| s   | 出力              | 記号  |

|-----|-----------------|-----|

| 000 | a               | THA |

| 001 | b               | THB |

| 010 | a AND b         | AND |

| 011 | a OR b          | OR  |

| 100 | a を 1 ビット左シフト   | SL  |

| 101 | a を 1 ビット論理右シフト | SR  |

| 110 | a+b             | ADD |

| 111 | a-b             | SUB |

|     |                 | )   |

yにa,bをそのまま出すのは奇妙な感じがするが、実はこれがないと周辺回路が面倒になるので、たいていのALUはこの機能を持っている。この命令をここではTHA(Z)ルーA)、THB(Z)ルーB)と呼ぶ。

さて、もちろん ALU の中には、加算器や AND のアレイが入っているのだが、最初は中身については考えず、とにかく com の値によって決った演算をやってくれることにする。このような考え方をブラックボックス化と呼ぶ。中身を知らなければ納得できない、という人は第4章に解説があるのでそちらをご覧いただきたい。

## 2.3 計算をするということ

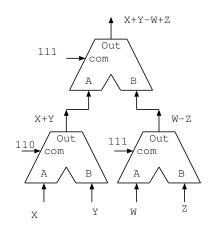

この ALU で X+Y を計算する場合、両方の入力に X と Y を入れ、s に 110 をセットすれば良い。では、もう少し複雑な

#### X+Y-W+Z

などの計算を ALU でどのように行えば良いのだろう。図 2.4 のように複数の ALU を組み合わせればこの演算を実現することができる。しかし、このようなことをしていくと、式が長くなると、どんどん利用しなければならない ALU 数が増えてしまう。

図 2.4: ALU の接続

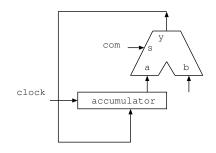

そこで、数を記憶しておく場所を設ける。これをレジスタ (register) あるいは置数 器と呼ぶ。抵抗器の resiter ではないので注意。店のレジと語源は同じである。これも 中身が気になる人は第4章を参照されたい。ここでは、入力したクロックがLから H に変化した際に、入力データを記憶する装置だと考えてほしい。

図 2.5 に示すように、ALU の片方の入力にレジスタの出力を入れ、レジスタの入力に ALU の出力を接続する。すなわち、計算結果をレジスタに格納し、それを再び ALU の入力として計算に使えるようにするわけである。

X+Y-W+Zをこのデータパスで実行するには以下のようにすれば良い。ここでは、一行分計算を実行した所でクロックを変化させてレジスタに値をセットすると考える。

| s   | b | クロック変化後のレジスタ |

|-----|---|--------------|

| 001 | X | X            |

| 110 | Y | X+Y          |

| 111 | W | X+Y-W        |

| 110 | Z | X+Y-W+Z      |

図 2.5: 最も簡単なデータパスの構成

このようにすると、ひとつの ALU を使い回すことが可能になる。計算結果はレジスタに置かれて、更新される。このレジスタは結果が積み重なる場所となり、アキュムレータ (accumlator) と呼ばれる。電卓で計算をする時、我々は無意識にこのアキュムレータの考え方を使っている。また、この一行め (com=001) は、最初に計算すべき値をアキュムレータにセットする役割を果たす。このように外部からレジスタに値をセットする操作をロード (load) 操作と呼ぶ。また、コンピュータで演算を行い、その途中結果を格納しておく部分をデータパス (datapath) と呼ぶ。

## 演習 2.4

図 2.5 のデータパスで X-Y+Z を計算したい。 com e b にどのような値を与えれば良いか。

## 2.4 メモリを使った計算

これまでのデータパスでは、アキュムレータを使うことで、演算した結果に対して 次々に演算を施して行くことができた。しかし、以下のような演算はスムーズに行う ことができない。

#### (SL X)+(SL Y)

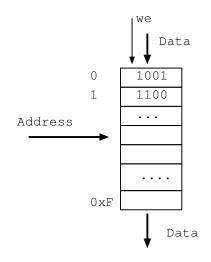

上の式ではまずXをアキュムレータに入れて1ビット左シフトし、その結果をどこかにとっておいて、それからYを左シフトして加えなければならない。つまり、結果をとっておく場所が必要であり、これを可能にするのがメモリである。電卓でもメモリ付きになっているのが普通で、このような枠組みは計算には必須である。

ここでは、メモリは単純に図 2.6 に示す表と考えて欲しい。この表は、各行に番号 (アドレス) が振られており、アドレスの値によって、対応する行の中身 (データ) を読み出すことができる。この場合、アドレスに 0 を設定すれば 1001 が、1 を設定すれば 1100 が読み出され、Dataout に出力される。

また、書き込みの場合、入力にデータを置き、アドレスを設定し、書き込み制御信号 we(write enable) を H にし、クロックを立ち上げると、そのアドレスにデータが書き込まれる。

この図は簡単で、幅が 4 ビットで深さが  $2^4$ =16 のメモリということになり、全容量は 64bit である。深さが 16= $2^4$  であるため、番地を識別するアドレス線も 4 本で良い。もちろん、実際のメモリはもっとずっと大きく、アドレスが 32bit-48bit、データは 32bit-64bit で膨大な情報量を格納する。しかし原理は同じである。アドレスが mbit あれば、 $2^m$  行分指定することができ、容量の大きいメモリほど、アドレスの本数も多い。ここでは、幅が 16bit、深さが 256 のメモリを考える。この場合、アドレスの本数は 8 本となる。

図 2.6: メモリの構成

それでは、このメモリを前回のデータパスにつないでみよう。この様子を図 2.7 に示す。

この構成では、データパスの入力にはメモリの出力、アキュムレータ出力にはメモリの入力が接続されている。すなわち、データを外から与えてやる代わりにメモリ中にあらかじめ格納してデータに対して演算を行い、途中結果もメモリに格納することができる。

## 2.4.1 命令の基礎

さて、このデータパスに外部から指示を命令の形で与えて計算をやらせよう。 まず演算を行うためには、メモリ中に存在するデータをアキュムレータに格納する 必要がある。コンピュータでは、このための命令を、

図 2.7: メモリ付きデータパス

## (持って来い) 0番地のデータを

の形で表す。日本語とは語順が逆なのは、命令を最初に作った人が英語を元に考えたからである。(持って来い)の部分、つまり操作を示す部分を命令コード (opcode,オペコード、オプコード) と呼ぶ。0番地のデータをに対応する操作対象を示す部分をオペランド (operand) と呼ぶ。

メモリからレジスタにデータを持って来いという意味は先に述べたように、英語でLoadである。(これは習慣で決っている。getでもtakeでもない。moveという場合もある。)命令としてはLoadと直接英語で書かずにLDという記号で書く。これをニーモニックと呼ぶ。本来、ニーモニックは命令セット毎に違うのだが、長年の蓄積で、ほぼ共通のコードを使っている。したがってLDと言ったら、情報系の人ならば万国共通で、メモリをレジスタに持ってくる命令だと分かる。オペランドの部分はここでは、単にメモリの番地に相当する。したがって、0番地のデータを持ってくる命令は

#### LD 0

と書く。これは、人間に分かりやすい形であって、アセンブリ言語表記あるいはアレンブラ表記と呼ぶ。コンピュータのハードウェアは、1/0 のパターンに対応付けたものを実行する。この場合、LD に 0001、アドレスはそのまま 0000 を割り当てると命令は以下のようになる。

**0001 00000000 // LD 0 0** 番地の内容を読み出してアキュムレータに格納 **0001 XXXXXXXX // LD X X** 番地の内容を読み出してアキュムレータに格納

これが機械語である。LD 命令が実行されると、オペランドがメモリのアドレスに与えられ、読み出されたデータは ALU の B 入力から Y 入力に抜ける。このためにALU のコマンドを 001 にセットする。そして、アキュムレータに書き込んでやる。

LD の逆の操作、すなわち、アキュムレータからメモリにデータを書き込む操作を Store と呼ぶ。これもニーモニックでは ST と書いてやる。ここでは、ST には 1000 を 割り当てることにしよう。オペランドは以前と同様でメモリのアドレスである。

```

1000 00000000 // ST 0 0番地にアキュムレータの内容を書き込む 1000 XXXXXXXX // ST X X番地にアキュムレータの内容を書き込む

```

ST 命令実行時には、メモリのアドレスにはオペランドを与え、アキュムレータから直接引かれているデータ線を用いて、データをメモリに書き込む。

## 2.4.2 演算命令

典型的な命令は演算命令である。これは、アキュムレータの内容とメモリの指定されたアドレスのデータを演算して、答えをアキュムレータに格納する。ここで使うALUは、6つの演算操作ができるので、以下の6命令が定義できる。命令コードはどう決めてもいいのだが、ここでは下3ビットをALUのcomと一致させ、最上位ビットを0として決めよう。オペランドは以前通りメモリの番地である。ここで、SL(左シフト、shift left)とSR(右シフト、shift right)は、B入力は使われないため、アドレスには何を入れても良い。(ドントケア)

```

0010XXXXXXXXX // AND X (X 番地とアキュムレータの内容を AND)0011XXXXXXXXX // OR X (X 番地とアキュムレータの内容を OR)0100------ // SL (アキュムレータの内容を左 1 ビットシフト)0101----- // SR (アキュムレータの内容を右 1 ビット論理シフト)0110XXXXXXXXX // ADD X (X 番地とアキュムレータの内容を加算)0111XXXXXXXX // SUB X (アキュムレータの内容から X 番地の内容を減算)

```

実はLDはこれらの演算命令の一種であったことに気づいただろうか?それでは、今まで定義した命令を使って、演算処理を実行してみよう。

#### 例題 2.3

X,Y,Z がそれぞれ 0,1,2 番地に格納されているとする。

Z=X+Y

は以下のような命令を順に実行すれば計算できる。

LD 0 0001 00000000 ADD 1 0110 00000001 ST 2 1000 00000010

では、以下はどうであろうか?

#### 例題 2.4

#### Z = X + Y - Z

これは、A+Bの結果がアキュムレータに残っているのでそれがそのまま使えるので簡単である。これがアキュムレータの良い点である。

LD 0 0001 00000000 ADD 1 0110 00000001 SUB 2 0111 00000010 ST 2 1000 00000010

しかし、最初に示した演算では、アキュムレータの値を直接利用することはできない。

## (X << 1) + (Y << 1)

この場合 X の 1 ビットシフトを計算し、その結果をどこかにとっておく必要がある。この中間結果をとっておく場所をここでは 2 番地としよう。

LD 0 0001 00000000

SL 0100 00000000

ST 2 1000 00000010

LD 1 0001 00000001

SL 0100 00000000

ADD 2 0110 00000010

ST 2 1000 00000010

2番地に一度中間結果を入れてから Y を LD し、シフトをした後、加算をする。入れる。これは、ちょうどメモリ付きの電卓を使う際に中間結果をメモリにとっておくのと似ている。

## 演習 2.5

0番地,1番地,2番地にそれぞれ A,B,C が格納されている。(A-B) OR (B+C) の演算を行い、3番地に答えを格納するプログラムをアセンブラ表記、機械語の両方で示せ。

## 2.5 Verilogでの記述

## 2.5.1 加算器の記述

Verilog では、一つのまとまりをもった回路をモジュールと呼ぶ。Verilog の記述は、まずモジュールの名前と入出力を定義することから始まる。

```

module 名前 (

input 入力 1,

input 入力 2,

output 出力 1,

output 出力 2 );

```

この定義の方法は、C言語の関数定義とちょっと似ているが、最後にセミコロン (;) が付いて文の形になっている点が違っている。まず a, b の 2 入力を持ち、s の出力を持つ 1bit の加算器の記述を示す。これは以下のように非常に簡単である。

```

/* 1 bit adder */

module adder (

input a, b, output s );

assign s = a + b ; // add a b

```

#### endmodule

コメントは C 言語同様 2 種類 (/\* \*/e//) が可能である。さて、加算器は、後の章に解説するようにリプルキャリアダーからプリフィックスアダーまで様々な構成があるが、Verilog でも VHDL でもここは抽象化して単に'+'で表す。どのような加算器を使うかは、後に論理合成の段階で、必要なコストと性能を考えて、自動合成用のCAD(Computer Aided Design) プログラムが選択する。設計者はこの選択時に必要な指示を与えてやる。s=a+b; の前に assign が付いているのに注意されたい。assign 文は、ある回路の出力ある端子に出力する、あるいは接続することを意味する。ここでは加算の結果をs に出力する、あるいは加算結果出力をs と接続することを示している。最後にモジュール文は endmodule で終わるが、ここは; は付かない。

この記述は adder.v というファイルに入れておく。C 言語のプログラムの拡張子が.c であるのと同様、Verilog-HDL 記述の拡張子は.v である。

次にこれをシミュレーションしてみよう。第1章に紹介したように、Verilog は元々シミュレーション記述用の言語であり、シミュレーションに対する指示の方法は多様で、理解するのが大変である。ここはまずは動かしてみるのが良いと思う。

下の test.v は上記の加算器のモジュールをテストするシミュレーション用の Verilog 記述である。この記述は、ハードウェアの回路を表すのではなく、テストするための入力の与え方と、出力の表示の仕方を示す。このような記述をテストベンチと呼ぶ。

Verilogを習得する時にやっかいなのは、テストベンチ中には結構難しい文法が必要とされるのに、これを書かないとテスト対象のモジュールがいかに簡単なものであっても全くシミュレーションができない点である。これを避けるためにある種の CAD では、パラメータを与えてテストベンチを自動生成する機能を持つ。

で、ここでは、テストベンチの解説は一応しておくが、重要な文法は後でまた解説することにして、直感的に理解する程度で深く突っこまないで先に進みたい。実の所、テストベンチの作り方は定型的なので、一定のパターンをマスターしてこれを場合に応じて修正すれば、かなりの範囲で応用が効く。どうか細部にこだわらず、大体の意味を掴んでほしい。

```

/* test bench */

'timescale 1ns/1ps

module test;

parameter STEP = 10;

reg ina, inb;

wire outs;

adder adder_1(.a(ina), .b(inb), .s(outs));

initial begin

$dumpfile("adder.vcd");

$dumpvars(0,adder_1);

ina <= 1'b0;

inb <= 1'b0;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b0;

inb <= 1'b1;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b1;

inb <= 1'b0;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b1;

inb <= 1'b1;

#STEP

```

```

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b0;

inb <= 1'b0;

$finish;

end

endmodule</pre>

```

最初に出てくるタイムスケール文は、シミュレーションの基本時間、時刻刻みの最小時間を定義する。

#### 'timescale 1ns/1ps

ここでは前者は  $1ns(ナノ=10^{-9}$  秒)、後者は  $1ps(ピコ=10^{-12}$  秒) とした。 次に、パラメータ文を使って今回シミュレーションを行う 1 ステップの時間を定義する。

## parameter STEP = 10;

このパラメータ文は実行時に外部から値を設定できるのがミソで、便利なので良く用いられる。ここでは10nsecを1ステップとする。

次に加算器に外部から値を与えるための入力、値を取り出すための出力用の端子を 定義してやる。ここで、入力には、値を保持するためレジスタ (reg) として宣言し、出 力は単に値を取り出せば良いので端子名を宣言 (wire) してやる。

```

reg ina, inb;

wire outs;

```

次に、adder モジュールの実体を定義して入出力を接続する。先にモジュール文で adder.v 内に定義した加算器のモジュール名を最初に指定し、次に実体名 (ここでは adder\_1) を宣言して実体を生成する。一つのモジュールから多数の実体を別の名前で 生成することができる。括弧内で、入出力の接続を行う。. の後にモジュール内の入出力名、() の中に接続する外部端子の名前を記述する。ここでは adder 内で宣言された a 入力に外部の ina を、b 入力に外部の inb を、s 出力に外部の outs を接続する。

```

adder adder_1(.a(ina), .b(inb), .s(outs));

```

これで宣言が終わりで、次は initial 文で、シミュレーションの動作を記述する。 initial 文は、開始後一回だけ begin から end までの文が順に実行される。

```

$dumpfile("adder.vcd");

$dumpvars(0,adder_1);

```

最初にのついた二つの文が実行される。Verilog 内では、シミュレーションを制御する上で必要な特殊なタスク (操作)を示す。この dumpfile と dumpvars では波形ビュアーで見るためのファイル名 (adder.vcd) と、信号を記録する範囲が指定されている。次にいよいよシミュレーションを開始する。

```

ina <= 1'b0;

inb <= 1'b0;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b0;

inb <= 1'b1;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b1;

inb <= 1'b0;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b1;

inb <= 1'b1;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);

ina <= 1'b0;

inb <= 1'b0;

$finish;

```

ina, inb への値の代入は、後に解説するノンブロック代入文 <= で行っている。これで 0,1 が順に設定される。#STEP は、10nsec の時間経過を示す。すなわち、以下の文は、

```

ina <= 1'b0;

inb <= 1'b0;

#STEP

$display("a:%b b:%b s:%b", ina, inb, outs);</pre>

```

まず、ina, inbに0を設定し、10nsec 時間が経過したら、ina, inb, outs を表示する、という意味である。さて、Verilog では定数を以下のように表現する。

<ビット幅>'<基数><数値>

基数は

- b:2進数

- h:16進数

- o:8 進数

である。なにも書かないと 10 進数になるので、数を直接書く際は、必ず桁数をはっきりさせて 2 進数、あるいは 16 進数で書くことをお勧めする。ここで 1 'b0 は 1 bit の 0 を、1 'b1 は 1 bit の 1 をそれぞれ示す。

\$display("a:%b b:%b s:%b", ina, inb, outs);

display 文はその名の通り、ina,inb,outs の値を表示するためのものである。display 文の記述は C 言語の printf に似ているが、2 進数を表示するための%b を持っている。また、自動的に改行が入る。以下、入力を変えて、それぞれ 10nsec 時間を経過させて結果を出力していく。最後は finish 文でシミュレーションを終了する。

## 2.5.2 シミュレーションの実行

では、シミュレーションをしてみよう。第1章で紹介した ikarus verilog をインストールしてある環境を想定する。

iverilog test.v adder.v

で、シミュレーションの実行形が生成される。シミュレーション自体は、

vvp a.out

で実行される。ここでは最初はa入力、次はb入力、最後に加算結果が出力される。a.out の名前が気になる方は、

iverilog test.v adder.v -o adder

vvp adder

としても良い。

a:0 b:0 s:0

a:0 b:1 s:1

a:1 b:0 s:1

a:1 b:1 s:0

が出力される。次に波形を見てみよう。テストベンチで記述した波形データを入れておくファイルを指定して立ち上げる。

図 2.8: gtkwave による波形表示

## gtkwave adder.vcd

左側のSSTと書いてある所にtestとテストベンチのモジュール名が表示されるのでそこをクリックすると adder\_1 という加算器の実体名が表示される。ここをクリックすると信号名が Signals ウインドウに表示される。ここで、見たい信号をクリックしてから Append をクリックすると、Waves ウインドウに波形が表れる。gtkwave を始めて使う時に戸惑うのは、Waves の設定が最小時刻刻みになっているため、最初のきわめて一部しか表示されない点である。Zoomの所の虫眼鏡の-を連打して表示スケールを調整すると、見たい範囲で波形が見られる。gtkwave は優れた GUI を持っているため、勘で結構使える。ここではあまり解説しないが、色々機能を試して欲しい。ちなみに終了の際は File→Quit で確認用の小ウインドウが出てくるので、ここで Yes を押してやる。

## 演習 2.6

adder の記述を書き換えて、減算、AND、OR などにして試してみよ (減算は実は加算 と同じになる)。

## 2.5.3 ALU の記述

次にやや難しい ALU を記述してみる。まず、1 ビットはあんまりなのでビット数を拡張することにしよう。ハードウェアでは配線を何本か束にして扱う場合が多い。これをバス (Bus) と呼び、Verilog では大括弧でくくって、MSB:LSB の形でその範囲を表わす。本書では簡単のため LSB は常に 0 としよう。

入出力 16 ビット、コマンド 3 ビットの ALU は次のように定義される。

#### module alu (

input [15:0] a, b,

input [2:0] com,

output [15:0] y );

次に中身を定義する。ALU の場合、入力が特定の条件ならば入力同士の演算の結果を出力する。このような場合、Verilog では以下のように記述する。

assign 出力 = 条件? 式1 : 式2;

条件が真であれば式1の結果が出力され、そうでなければ式2の結果が出力される。 条件を複数書くこともできる。これは case 文と似ている。条件は前から順にチェック されるので、優先順位は先に書いた方が高いことになる。下の例では、条件1-3 がど れも真でなれば、コロンの後に書いた式4の結果が出力される。

assign 出力 = 条件 1? 式 1 : 条件 2? 式 2 : 条件 3? 式 3 : 式 4;

今回の ALU は、以下のような機能を定義した。

| com | 出力              | 記号  |

|-----|-----------------|-----|

| 000 | a               | THA |

| 001 | b               | THB |

| 010 | a AND b         | AND |

| 011 | a OR b          | OR  |

| 100 | a を 1 ビット左シフト   | SL  |

| 101 | a を 1 ビット論理右シフト | SR  |

| 110 | a+b             | ADD |

| 111 | a-b             | SUB |

これを Verilog 記述すると、以下のようになる。

assign y = com==3'b000 ? a: com==3'b001 ? b: com==3'b010 ? a & b: com==3'b011 ? a | b: com==3'b100 ? a<<1: com==3'b101 ? a>>1: com==3'b110 ? a + b: a - b ;

Verilog は、表 2.1 に示す演算を記述できる。ここでは AND, OR, 左右のシフト、加算、減算を使っている。AND, OR では、16 ビットの入力のそれぞれの桁同士で演算が行われ、答えも 16 ビットになる。

ここで、論理演算は、C言語で用いるのと同様に、条件の論理的な真偽に対する演算を行い、結果は1ビットの値となる。ここでは比較演算子==を使っている。比較対象は3ビットの2進数なので、3'b000と書く。

演算子には優先順位があるので注意されたい。表 2.2 で上位にあるもの程強い。

| 衣 2.1. VCIIIOg の至年時便昇 J |      |                 |  |  |  |

|-------------------------|------|-----------------|--|--|--|

| ビット演算                   | ~    | NOT             |  |  |  |

|                         | &    | AND             |  |  |  |

|                         | ~&   | NAND            |  |  |  |

|                         |      | OR              |  |  |  |

|                         | ~    | NOR             |  |  |  |

|                         | ^    | Ex-OR           |  |  |  |

|                         | ~^   | Ex-NOR          |  |  |  |

| シフト演算                   | <<   | 左シフト            |  |  |  |

|                         | >>   | 右シフト            |  |  |  |

| 等号、関係演算                 | ==   | 等しい             |  |  |  |

|                         | ! =  | 等しくない           |  |  |  |

|                         | ===  | 等しい (x,z も比較)   |  |  |  |

|                         | ! == | 等しくない (x,z も比較) |  |  |  |

|                         | <    | 小さい             |  |  |  |

|                         | <=   | 以下              |  |  |  |

|                         | >    | 大きい             |  |  |  |

|                         | >=   | 以上              |  |  |  |

| 算術演算                    | +    | 加算              |  |  |  |

|                         | _    | 減算              |  |  |  |

|                         | *    | 乗算              |  |  |  |

|                         | /    | 除算              |  |  |  |

|                         | %    | 剰余算             |  |  |  |

| 論理演算                    | !    | 否定              |  |  |  |

|                         | &&   | 論理積             |  |  |  |

|                         |      | 論理和             |  |  |  |

表 2.1: Verilog の基本的演算子

## 2.5.4 define 文を使って格好を付ける

先に示した ALU の記述はきちんと動作し、合成もできるが、あまり格好良いと見なされない。これは、コード中に 3'b000 とか 15:0 など定数が直に記述されているからである。これらのハードウェアの記述に必要な定数 (マジックナンバーと呼ばれることもある) は、直接コード内に書かない方が良い。これは、コードが読みにくくなることと、仕様変更があった際にコード中のあちこちを変更しなければならないためである。そこで、Verilog では C 言語と同様 define 文でこれらの定数をあらかじめ定義しておく。ただし C 言語と違って define 文の前と定義された文字列を使う場合はバックシングルコーテーション (') を使う。下記は 4 種類の演算のみこの変換を行った例である。

表 2.2: 基本的演算子の優先順位

```

高い ^~!&|+-(単項演算子)

*/%

+-

<<>>><<>>>

<=>=!===!==

&~&~~^

| ~|

&&&

||

低い

```

## 演習 2.7

上記の記述を全ての演算について行え。

define 文は parameter 文よりも変更が少なく、基本的に決めたら滅多に変えないものを定義するのに使う。ただ両者の特徴は微妙で、これについては、web のうんちくを参照されたい。

## 2.5.5 ALU のテストベンチ

下の test.v は ALU をテストするシミュレーション用のテストベンチである。基本的なやり方は、加算器用と同じである。

```

/* test bench */

'timescale 1ns/1ps

'define DATA_W 16 // bit width

'define SEL_W 3 //control width

'define ALU_THA 'SEL_W'b000

'define ALU_THB 'SEL_W'b001

'define ALU_AND 'SEL_W'b010

'define ALU_ADD 'SEL_W'b110

module test;

parameter STEP = 10;

reg ['DATA_W-1:0] ina, inb;

reg ['SEL_W-1:0] sel;

wire ['DATA_W-1:0] outs;

alu alu_1(.a(ina), .b(inb), .s(sel), .y(outs));

initial begin

$dumpfile("alu.vcd");

$dumpvars(0,alu_1);

ina <= 'DATA_W'h1111;

inb <= 'DATA_W'h2222;</pre>

sel <= 'ALU_THA;</pre>

#STEP

$display("a:%h b:%h s:%h y:%h", ina, inb, sel, outs);

sel <= 'ALU_THB;</pre>

#STEP

$display("a:%h b:%h s:%h y:%h", ina, inb, sel, outs);

sel <= 'ALU_AND;</pre>

#STEP

$display("a:%h b:%h s:%h y:%h", ina, inb, sel, outs);

sel <= 'ALU_ADD;</pre>

#STEP

$display("a:%h b:%h s:%h y:%h", ina, inb, sel, outs);

$finish;

```

end

## endmodule

今回は、桁数が 16bit になっており、a,b 入力には 16 進数を、com には 2 進数を使って定義をしている点に注意されたい。16 進表示は C 言語の 0x ではなく 16 を使う。

a <= 16'h1111; b <= 16'h2222; com <= 3'b000

同様に、display 文も 16 進表示は%x でなくて、%h である。では、加算器と同様に シミュレーションをしてみよう。

## iverilog test.v alu.v

で、シミュレーションの実行形が生成される。シミュレーション自体は、

## vvp a.out

で実行される。ここでは最初はa入力、次はb入力、最後に加算結果が出力される。

a:1111 b:2222 com:0 y:1111 a:1111 b:2222 com:1 y:2222 a:1111 b:2222 com:6 y:3333

## 演習 2.7

AND,OR,減算のシミュレーションを行い、結果を確認せよ。

## 2.5.6 データパスの記述

図 2.5 のデータパスを記述してみよう。このためには、レジスタを記述する必要がある。レジスタはクロックに同期してデータを格納する点でやや特殊な素子であり、ALU での論理演算とは雰囲気が違っている。

Verilog でレジスタを宣言する際はそのものずばり

## reg [15:0] acum;

とすれば良い。ここでのアキュムレータは 16 ビットのデータを記憶するので、入出力同様バスの形にして宣言する。図 2.5 を見ると、信号線を区別するため alu\_y などの名前が付いている。Verilog では、wire 文で信号の名前を宣言する。

## wire [15:0] alu\_y;

レジスタと違って、alu\_y は ALU の出力データそのものを示していて、データを記憶することはできない。ALU 同様、直接数字を書かないことにして、ここでは、

```

reg ['DATA_W-1:0] accum;

wire ['DATA_W-1:0] alu_y;

```

と記述する。ここで ALU の時と違って、この define 文を 1ヶ所にまとめて def.h としておく。そして

'include ''def.h''

とすれば、様々なファイルで同じ定義を共有することができる。この辺の発想は、 C言語と同じである。ただし、include 文の先頭にはシングルバックコーテーション (')が付く点に注意されたい。def.h の中身は以下の通りである。

```

'define DATA_W 16

'define SEL_W 3

'define ADDR_W 8

'define DEPTH 256

'define ALU_THA 'SEL_W'b000

'define ALU_THB 'SEL_W'b001

'define ALU_AND 'SEL_W'b010

'define ALU_ADD 'SEL_W'b110

'define ALU_SUB 'SEL_W'b111

'define ENABLE 1'b1

'define DISABLE 1'b0

'define ENABLE_N 1'b0

'define DISABLE_N 1'b1

```

では、全体の記述を見てみよう。

```

'include "def.h"

module datapath(

input clk, input rst_n,

input ['DATA_W-1:0] datain,

input ['SEL_W-1:0] com,

output ['DATA_W-1:0] accout);

reg ['DATA_W-1:0] accum;

wire ['DATA_W-1:0] alu_y;

```

```

assign accout = accum;

alu alu_1(.a(accum), .b(datain), .s(com), .y(alu_y));

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) accum <= 'DATA_W'b0;

else accum <= alu_y;

end

endmodule</pre>

```

このデータパスは、アキュムレータの中身をメモリに書き込むために外部に出さなければならない。このような場合、assign文を用いる

## assign accout = accum;

この文は、accum のデータを dataout に出力すると考えてもよいし、accum を出力 dataout に接続すると考えても良い。さて、ALU は別モジュールとして宣言されているので、これを部品として使う。これが以下の記述である。

alu alu\_1(.a(accum), .b(datain), .com(com), .y(alu\_y));

alu がモジュール名であり、alu\_1 が実体 (インスタンス) 名である。同じモジュールから実体を多数作ることも良く行われる。先に述べたように、Verilog では、モジュール内の入出力名を.(ピリオド) で表し、それに接続する外部信号名を括弧の中に書いて対応を付ける。つまり、ALU の a 入力には accum を、b 入力には datain を、com 入力には com を接続し、y に alu\_y を接続して出力を取り出す。ここで、com は内部も外部も同じ名前を使っているが、module alu と module datapath の両方で宣言されていれば問題ない。

## always @(posedge clk) accum <= alu\_y;</pre>

最後の部分が、アキュムレータ accum に ALU 出力 alu\_y を覚えさせる記述である。 この書き方がとっつきにくいのが、Verilog が入門者に嫌われる理由の一つになっているが、決った使われ方しかしないので、「おまじない」と思えば良い。

コンピュータでは、レジスタやメモリにデータを覚えさせるのは、一定の信号の変化に合わせて行なう。この信号をシステムクロックあるいは単にクロックと呼ぶ。3GHzで動作する CPU とか呼ぶが、これはクロックの周波数を示している。これが高い程、CPU は高速で動くので宣伝文句として使われる。3

さて、

<sup>3</sup>しかしクロック周波数は性能と直接結びつかないので注意。これは後に取り上げる

## always @(posedge clk)

は、always=いつも、@=at つまり.. の時、(posedge clk)=クロックが L レベルから H レベルに変化する (立ち上がり:positive edge) という意味である。つまり、「clk の立ち上がりの時にはいつも」ということを示す。ちなみに立ち下がりで動作する際は、negedge:negative edge を使う。

## accum <= alu\_y;</pre>

<= は、ノンブロッキング代入文と呼び、レジスタにデータを覚えさせる時に使う。先のテストベンチでも使っていた。ここには同じクロックの立ち上がりで動作する複数の文を begin end で使って書くことができる。これは後に紹介する。

## 2.5.7 データパスのシミュレーション

ここまでのデータパスにはメモリが含まれていない。後に解説するがメモリは普通は論理合成の対象としないため、テストベンチの中に入れて記述しよう。メモリはレジスタ同様 reg 文で記述するが、名前の後に

最初の番地:最後の番地

の形で、記憶できる範囲を示す。

## reg [15:0] dmem [0:15];

この場合、dmem は 0 番地から 15 番地まで記憶できるアドレスを 16 持つ。ということはアドレスは 4 ビットで表すことができる。

## reg [15:0] dmem [0:1023];

と書けば、1024=1Kの範囲で、アドレスは10本になる。原則として範囲は2のべき乗で示す。メモリからの読み出しは、4ビットのdaddrを宣言しておき、それを直接括弧の中い入れれば良い。

## dmem [daddr];

書き込みはレジスタ同様 always 文を用いるが、メモリは、データを書き込む場合と、何も書き込まず単に読み出しだけを行う場合があるので、we(write enable) 端子でこれを指示する。we=1 とした時のクロックの立ち上がり時にデータが書き込まれる。そこで、記述は下のようになる。

## always @(posedge clk)

if(we) dmem[daddr] <= ddataout;</pre>

if 文は C 言語など多くのプログラミング言語と同様、括弧内の条件が真になった時に次に書く動作が実行される。最初は奇妙に思われるかもしれないが Verilog は always 文など限られた構造の中でのみ、if 文の利用が許される。

さて、このメモリの記述を含むデータパスのテストベンチは以下のようになる。

```

/* test bench */

'timescale 1ns/1ps

'include "def.h"

module test:

parameter STEP = 10;

reg clk, rst_n;

reg ['DATA_W-1:0] datain;

reg ['SEL_W-1:0] com;

reg ['ADDR_W-1:0] addr;

reg we;

wire ['DATA_W-1:0] accout;

wire ['DATA_W-1:0] dmem2;

reg ['DATA_W-1:0] dmem ['DEPTH-1:0];

always @(posedge clk)

begin

if(we) dmem[addr] <= accout;</pre>

end

always #(STEP/2) begin

clk <= ~clk;

end

datapath datapath_1(.clk(clk), .rst_n(rst_n), .com(com),

.datain(dmem[addr]), .accout(accout));

initial begin

$dumpfile("datapath.vcd");

$dumpvars(0,test);

$readmemh("dmem.dat", dmem);

clk <= 'DISABLE;</pre>

rst_n <= 'ENABLE_N;</pre>

{we,com,addr} <= {'DISABLE,'ALU_THB,'ADDR_W'h00}; // LD 0</pre>

\#(STEP*1/4)

#STEP

rst_n <= 'DISABLE_N;</pre>

$display("we:%b com:%h addr:%h accout:%h", we, com, addr, accout);

```

```

$display("dmem[0]:%h dmem[1]:%h dmem[2]:%h", dmem[0], dmem[1], dmem[2]);

#(STEP*1/2)

{we,com,addr} <= {'DISABLE, 'ALU_ADD, 'ADDR_W'h01}; // ADD 1</pre>

#(STEP*1/2)

$display("we:%b com:%h addr:%h accout:%h", we, com, addr, accout);

$display("dmem[0]:%h dmem[1]:%h dmem[2]:%h", dmem[0], dmem[1], dmem[2]);

#(STEP*1/2)

{we,com,addr} <= {'DISABLE,'ALU_ADD,'ADDR_W'h02};</pre>

// ADD 2

#(STEP*1/2)

$display("we:%b com:%h addr:%h accout:%h", we, com, addr, accout);

$display("dmem[0]:%h dmem[1]:%h dmem[2]:%h", dmem[0], dmem[1], dmem[2]);

#(STEP*1/2)

{we,com,addr} <= {'ENABLE,'ALU_THA,'ADDR_W'h02};</pre>

#(STEP*1/2)

$display("we:%b com:%h addr:%h accout:%h", we, com, addr, accout);

$display("dmem[0]:%h dmem[1]:%h dmem[2]:%h", dmem[0], dmem[1], dmem[2]);

#(STEP*1/2)

{we,com,addr} <= {'DISABLE,'ALU_THA,'ADDR_W'h02}; // NOP</pre>

#(STEP*1/2)

$display("we:%b com:%h addr:%h accout:%h", we, com, addr, accout);

$display("dmem[0]:%h dmem[1]:%h dmem[2]:%h", dmem[0], dmem[1], dmem[2]);

$finish;

end

endmodule

まず、クロック信号 clk が一定の間隔で L,H,L,H を繰り返すようにしている。これ

が下記の文である。

always #(STEP/2) begin

clk <= ~clk;

end

```

この場合、STEP の半分で反転するということは、2回反転すればもとのレベルに 戻ることから、クロック周期はSTEPとなることがわかる。この記述でクロックを発 振させるには、clk を reg で定義して、初期化する必要がある。

initial 文以降は以前の記述と似ているが、データメモリに初期値を設定するための 文が必要である。

\$readmemh("dmem.dat", dmem);

この場合、データメモリの実体 dmem に対して dmem.dat という名前のファイル中の 16 進データ (readmemh だから) が初期設定される。あらかじめ dmem.dat に以下のフォーマットでデータを入れておく。

0002

0003

0004

0001

ちなみに、2 進数のデータを読み込むためには、readmemb を用いる。dmem.dat は シミュレーションを起動するディレクトリに置いておく必要がある。次に、以下の記述に注目されたい。

{we,com,addr} <= {'DISABLE,'ALU\_THB,'ADDR\_W'h00};</pre>

Verilog では中括弧は、信号をくっつけて一つにして扱うことを示す。すなわち、we,com.addr はこの順番にくっついて一連の信号線として扱われる。ここでは、we=0, com=001, addr=0000 が設定される。この場合、データパスに対する命令を操作の部分とアドレスの部分に分離している。ここでは、一定の時間間隔で、LD 0, ADD 1, ADD 2, ST 2 の命令が順に与えられる。このため、2+3+4=9 が dmem[2] に入る。

それぞれの display 文で、クロックが立ち上がる度に、アキュムレータの値とメモリの 0-2 番地を表示する。最初に STEP\*1/4 としているのは、値を設定する時刻と表示する時刻をクロックの立ち上がりとずらしてやるためである。シミュレーション上完全に同じ時刻に行うという指定をすると、どのような順番でシミュレーションが実行されるかわからなくなるため、困ったことになる。これを防ぐためである。

先ほどと同じように、

iverilog test.v datapath.v alu.v

vvp a.out

と打ち込みシミュレーションを行い結果が正しいことを確認せよ。

#### 演習 2.8

$A ext{ $e ext{ } 0$}$  番地、 $B ext{ $e ext{ } 1$}$  番地のデータとして、(SR A) OR (SR B) のデータを 2 番地にしまう命令の実行をテストベンチを改造してシミュレーションせよ。

#### 演習 2.9

## 演習 2.10

このデータパスは、ST 命令の実行時にも accum 中のデータが壊されずに動作する。これはなぜだろう?

## 第3

# アキュムレータマシン

## 3.1 アキュムレータマシンの構成

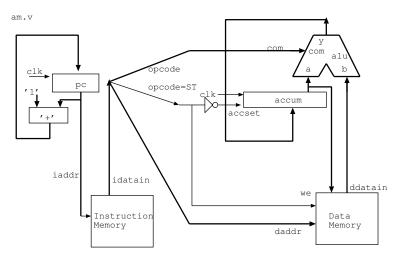

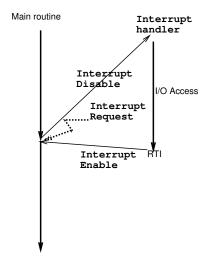

## 3.1.1 命令メモリと pc

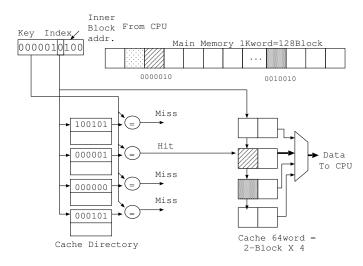

2章のデータパスでは、計算するデータはデータメモリにあらかじめ入れておけば良いのに、命令は外からクロックに合わせて与えてやらなければならず、これは大変である。そこで、データ同様、命令もあらかじめメモリに入れておき、これを順番に読み出してデータパスに与えるようにすれば便利である。この構成を図 3.1 に示す。ここでは、8 ビット× 256 エントリの命令メモリ (Instruction Memory) を想定し、この中に命令が並んで格納されていると想定しよう。例えば前回の C=A+B を計算するプログラムが以下のように入っている。

0 番地LD00001000000001 番地ADD10110000000012 番地ST2100000000010

ここで、命令を順番に実行するためには、現在実行しているプログラムの番地を保持しているレジスタが必要である。このレジスタをプログラムカウンタ PC(Program Counter) と呼ぶ。今、命令メモリは 256 エントリを持つので、PC は 8 ビットあれば良い。計算機は、以下の動作を繰り返す。

- 1. PC の指し示す命令を取ってくる(命令フェッチ)同時に PC に1を加える

- 2. 解読し (命令デコード)、

- 3. 前回定義したデータパス上でこれを実行する(命令実行)。その後1に戻る

前回の Verilog の実装では、ST 命令実行時には com=000(THA:スルー A) とすることで、アキュムレータに自分自身の値が書き込まれて、データが変化しなかった。し

かし、この方法では accum に値を書き込まない時は常に com=000 にしなければならず、命令数を増やすことができない。そこで、特定の命令でのみ accum に値を書き込み、それ以外では書き込まないようにしてやる。このために、accum に accset というセット入力を与えてやり、これが 1 の時のみ、結果を書き込むようにする。

図 3.1: アキュムレータマシンの構成

この構成が、プログラム格納型計算機の第一歩で、アキュムレータマシンと呼ばれる。

## 3.1.2 アキュムレータマシンの動作

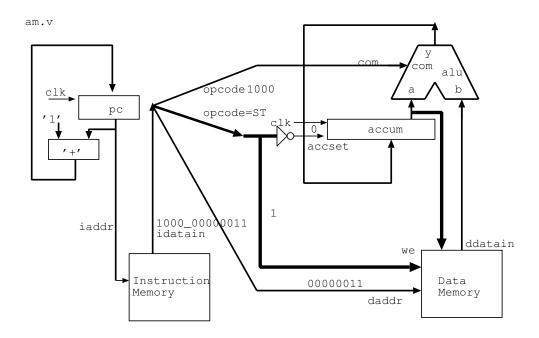

図 3.1 の動作を追ってみよう。まず、命令メモリ (Instruction Memory) のアドレスには pc が繋がっており、この内容の示すアドレスの命令が読み出さる。

読み出された命令が ST 命令以外ならば、Data memory から命令中の下位 8 ビットをアドレスとしてデータが読み出される。つまり LD 1 ならば 1 がアドレスに載る。そして読み出されたデータは ddatain から alu の b 入力に入る。alu の s 入力には、opcode の下位 3 ビットが入っている。LD 命令の場合、opcode は 0001 なので、com は 001 となり、THB が実行されて、読み出されて B 入力に入ったデータが、クロックの立ち上がりで、そのまま accum にセットされる。同時に pc には pc+1 がセットされ、次の番地の命令が指し示される。

読み出された命令が ADD 2 ならば、opcode は 0110 なので、com には 110 が与えられ、alu は a 入力と b 入力の加算を行う。a 入力には accum の値が常に入力され、b 入力は 2 番地から読み出したデータがやってくる。加算結果は EX 状態の終わりに accum に書き込まれる。

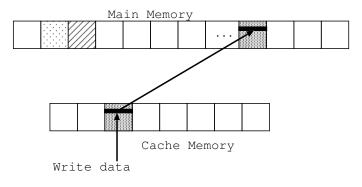

図 3.2: ST 命令の実行例

メモリへの書き込みを行う ST 命令でのみ、データパスの動作はやや異なっている。 ST 3 を実行する場合を図 3.2 に示す。ST 命令のアドレスは 00000011 であるので、最上位が 1 ならば ST 命令であるという判断ができる。ここで、Data memory の入力ポートには常に accum の出力が dataout を経由して接続されている。アドレスは他の命令同様、operand の値が与えられるため、この場合は 3 である。ここで we を H にすることで、data memory に accum の値を書き込む。

今の所、以下の命令が利用可能である。X は番地の2 進数を示し、-は使われないので何でも良いこと(ドントケアと呼ぶ)を示す。

ニーモニック 機械語 意味 NOP **0000** ----: No Operation: 何もしない 0001 XXXXXXXX: Load X: acc-m<- X 番地中の値 LD X AND X 0010 XXXXXXXX: AND X: acc-m <- acc-m AND X 番地中の値 OR X 0011 XXXXXXXX: OR X: acc-m <- acc-m OR X 番地中の値 SL 0100 -----: Shift Left: acc-m <- acc-m <1 0101 -----: Shift Right: acc-m <- acc-m>>1 SR ADD X 0110 XXXXXXXX: Add X: acc-m <- acc-m + X番地中の値 0111 XXXXXXXX: S-b X: acc-m <- acc-m - X 番地中の値 SUB X ST X 1000 XXXXXXXX: Store X: accum -> X 番地中

ここで、NOP はアキュムレータの値が自分自身に書き込まれるため、何もしない命令である。何もしない命令なんて意味があるんだろうか?と思われるかもしれないが、実はこの命令は時間稼ぎのために重要で、全てのコンピュータで装備されている。

#### 演習 3.1

0 番地の内容から 1 番地の内容を引き算し、2 番地に格納する操作を実行するプログラムを書け。

#### 演習 3.2

0番地の内容から1番地の内容を引き算した結果に、2番地の内容と3番地の内容を加算した結果とORするプログラムを書け。

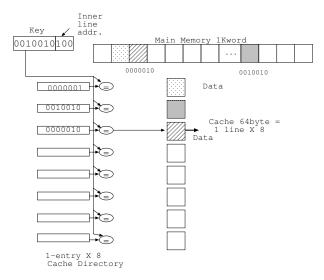

## 3.1.3 分岐命令

さて、このアキュムレータマシンは、命令メモリに格納された命令を順番に実行するに過ぎない。前の章の演習プログラムとて、実行が終わったら、次の番地の命令の実行に移ってしまう。完全な猪突猛進型で、演算処理の終了後に、停止することすらできない。

これではあらかじめ必要な処理に対応する命令を全て並べておかなければならず、ちっとも便利ではない。コンピュータが便利なのは、膨大な繰り返し処理をやってくれることと、結果に応じて判断して、実行する処理を変えてくれることである。これにより、プログラムを作って複雑なアルゴリズムを実行させることができる。つまり、「判断」して「処理を繰り返す」という命令が必要だ。

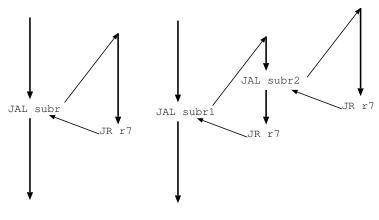

一定の処理を繰り返し実行させるためには、アキュムレータの内容を判断し、PC の内容を変更する命令を設ければよい。これを分岐命令(Branch)と呼ぶ。ここでは以下の命令を想定する。

BEZ X アキュムレータの内容が0ならば、PCをXXXXXXXX にする。 1001 XXXXXXXX BNZ X アキュムレータの内容が0でなければ、PCをXXXXXXXXX にする。1010 XXXXXXXXX

例えば BNZ 0 を実行すると、アキュムレータの内容が 0 でなければ、PC が 0 になり、次は 0 番地の命令を実行することになる。これをコンピュータ屋は「0 番地に飛ぶ」と言う。この場合アキュムレータの内容が 0 でなければ、分岐命令は何も行わず、次の番地の命令が実行される。

以下の命令が順に実行される場合を想定しよう。

| 0 | LD 0  | 0001 00000000 |  |

|---|-------|---------------|--|

| 1 | ADD 1 | 0110 00000001 |  |

| 2 | ST 0  | 1000 00000000 |  |

| 3 | LD 2  | 0001 00000010 |  |

| 4 | SUB 3 | 0111 00000011 |  |

| 5 | ST 2  | 1000 00000010 |  |

| 6 | BNZ 0 | 1010 00000000 |  |

| 7 | BEZ 7 | 1001 00000111 |  |

ここでデータメモリには、

- 0 0000

- 1 0002

- 2 0003

- 3 0001

が格納されているとする。何が起こるか考えて見よう。最初に3命令で、0番地の内容←0番地の内容+1番地の内容が実現できる。0番地の内容は0に初期化しておくことに注意。次の3命令で、2番地の内容←2番地の内容−3番地の内容が実行される。ここで3番地は1に初期化されているため、この3命令は2番地の内容から1を引いて書き戻すことになる。ここで、アキュムレータの内容が0ならば0番地に戻ることになる。つまり、このプログラムは2番地から1つづつ引きながら0になるま

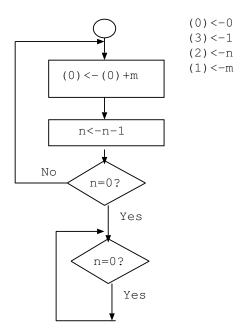

で1番地の内容を0に足し続ける。2番地が0になると、プログラムは7番地に飛び続けることで停止する(このような止め方をダイナミックストップと呼ぶ)。つまりこれは掛け算のプログラムであることがわかる。ここでは1番地に2が、2番地に3が格納されているので、 $2 \times 3$  が実行され、0 番地が6になる。アセンブラのプログラムは単純で原始的なので、図3.3に示すような流れ図を作って考えるとよい。

図 3.3: 掛け算プログラムの流れ図

分岐命令を実行するためには、(1)命令メモリから読み出した命令が分岐命令であり、(2)条件が成立する場合に限り、PCに命令の下位8ビットの飛び先をセットできるようにすれば良い。

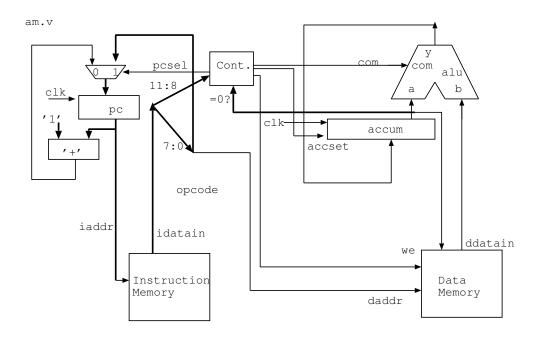

図 3.4 にこの改造したアキュムレータマシンのハードウェア構成を示す。台形印は、マルチプレクサあるいはデータセレクタというハードウェアモジュールで、この場合、2 つの入力の片方を、選択信号 pcsel に応じて選んで出力する。ここでは、pcsel=1 ならば、pc に operand を送り、S=0 ならば、pc には以前通り pc+1 を送る。マルチプレクサは、今後データパスを複雑にしていく場合不可欠なものである。また、accum には、accset 信号を L にして、分岐命令実行時にはデータをセットしないようにしてやる。この辺は ST 命令と同様である。太線に BEZ, BNZ 実行時のデータの流れを示す。まとめると、命令コードと S accumの値に応じて S pcsel, S accset, S we, S com S の値を以下のように制御する必要がある。

• ALU 演算命令 (LD,NOP を含む): accset=1, pcsel=0,we=0, com:opecode の下位 3

図 3.4: アキュムレータマシンの構成 (分岐命令付き)

ビット

- ST 命令:accset=0, pcsel=0,we=1,com:ドントケア

- 分岐命令: accset=0, pcsel:条件が成立すれば 1、そうでなければ 0、we=0、com: ドントケア

この信号はコントローラ (Cont) で生成される。コントローラはここでは非常に簡単な組み合わせ回路で済むが、命令が増えるにつれて複雑になっていく。

### 演習 3.3

今、1番地にAという数が格納されているとする。1+2+…Aを計算して0番地(あらかじめ0に初期化されている)に格納するプログラムを書き、機械語に変換せよ。ここでは例題同様、3番地は1という数字で初期化されているとする。

#### アキュムレータマシンの命令コード

本章のアキュムレータマシンの命令コードをまとめる。

```

NOP

0000 ----: No Operation: 何もしない

LD X

0001 XXXXXXXX: Load X: acc-m<- X 番地中の値

AND X

0010 XXXXXXXX: AND X: acc-m <- acc-m AND X 番地中の値

OR X

0011 XXXXXXXX: OR X: acc-m <- acc-m OR X 番地中の値

SL

0100 -----: Shift Left: acc-m <- acc-m<<1

0101 -----: Shift Right: acc-m <- acc-m>>1

SR

0110 XXXXXXXX: Add X: acc-m <- acc-m + X番地中の値

ADD X

SUB X

0111 XXXXXXXX: S-b X: acc-m <- acc-m - X 番地中の値

ST X

1000 XXXXXXXX: Store X: accum -> X 番地中

BEZ X アキュムレータの内容が0ならば、PC を XXXXXXXX にする。

BNZ X アキュムレータの内容が O でなければ、PC を XXXXXXXX にする。1010 XXXXXXXXX

```

## 3.2 アキュムレータマシンの Verilog 記述

## 3.2.1 Verilog 記述の解説

図 3.1 の verilog 記述を説明しよう。分岐命令がないのでまだコンピュータとは言えないことからモジュール名は datapath2 となっている。ここでは、図の構造がほとんどそのままの形で記述されている。命令メモリから読み出された来た命令 (idatain) は、opcode と operand に分離される。この opcode が ST 命令 (4'b1000) のときに書き込みが行われるようにしている。逆に accum には、ST 命令以外で alu で演算された

値が格納されるようになっている。pc はリセット時に 0 になり、後は順に 1 ずつ増えて行く。すなわち、0 番地から順に命令が実行される。

```

'include "def.h"

module datapath2(

input clk, input rst_n,

input ['OPCODE_W-1:0] opcode,

input ['DATA_W-1:0] ddatain,

output we,

output ['ADDR_W-1:0] pcout,

output ['DATA_W-1:0] accout);

reg ['DATA_W-1:0] accum;

reg ['ADDR_W-1:0] pc;

wire ['DATA_W-1:0] alu_y;

assign we = (opcode == 'OP_ST);

assign accout = accum;

assign pcout = pc;

alu alu_1(.a(accum), .b(ddatain), .s(opcode['SEL_W-1:0]), .y(alu_y));

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) pc <= 0;

else pc <= pc + 1;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) accum <= 0;</pre>

else if(opcode !='OP_ST) accum <= alu_y;</pre>

end

endmodule

ここでは、一つだけ新しい構文が出てくる。それは、

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) pc <= 0;

```

```

else pc \le pc + 1; end

```

の部分である。

今回のアキュムレータマシンにはリセット入力が付いている。ご存じと思うが、すべての CPU にはリセットボタンが付いていて、これを押すとシステムは初期化されてしまう。無闇に初期化するとデータを破壊する可能性があるので、このボタンは目立たない所にあって長時間押していないとリセットが掛からないようになっている。我々のアキュムレータマシンにもこのリセット入力が付くわけだが、ここでは、リセット信号線が L の時、リセットが掛かるようになっている。このような信号線をアクティブ-Lと呼び、ことでは信号名の後ろに\_nを付けて区別する。ちなみに多くのディジタル回路でリセット入力がアクティブ-L¹なので、このアキュムレータマシンもこの習慣に従っている。

さて、プログラムカウンタ pc は、リセット時に 0 にしておく必要がある。このための記述が always @(posedge clk or negedge rst\_n) である。ここでは、clk が 0 から 1 に変化する (立ち上がる:posege) か (or)、rst\_n が 1 から 0 に変化する (たちさがる:negedge) 時 (@:at) はいつでも (always)、リセットが掛かる記述になっている。これを非同期リセットと呼ぶ。リセット時の動作は、if 文の中に記述され、今回は単に pc を 0 にしている。ちなみにリセットには同期と非同期があるが、ここでは非同期リセットしか使わない $^2$ 。

もう一つ分かりにくいかと思う記述は、alu モジュールを利用する部分である。

alu alu\_1(.a(accum), .b(ddatain), .s(opcode['SEL\_W-1:0]), .y(alu\_y));

今回、ALU の制御入力 s には、opcode の下位 3bit を入れる必要がある。ここでは、SEL\_W は def.h の define 文で 3 にしてあり、コロン:で書いた範囲のビット、すなわち 2:0 が切り出されて、s に接続される。

では次に、これをテストするテストベンチ test.v を解説しよう。

```

/* test bench */

'timescale 1ns/1ps

'include "def.h"

module test;

parameter STEP = 10;

reg clk, rst_n;

wire ['DATA_W-1:0] ddataout ;

wire ['ADDR_W-1:0] pcout;

wire ['OPCODE_W-1:0] opcode;

```

<sup>1</sup>理由については web の解説を参照

<sup>&</sup>lt;sup>2</sup>理由については web の解説を参照

```

wire ['ADDR_W-1:0] operand;

wire we;

reg ['DATA_W-1:0] dmem ['DEPTH-1:0];

reg ['INST_W-1:0] imem ['DEPTH-1:0];

assign {opcode, operand} = imem[pcout];

always #(STEP/2) begin

clk <= ~clk;</pre>

end

always @(posedge clk)

if (we) dmem[operand] = ddataout;

datapath2 dp2(.clk(clk), .rst_n(rst_n), .pcout(pcout), .accout(ddataout),

.opcode(opcode), .we(we), .ddatain(dmem[operand]) );

initial begin

$dumpfile("datapath2.vcd");

$dumpvars(0,test);

$readmemh("dmem.dat", dmem);

$readmemb("imem.dat", imem);

clk <= 'DISABLE;</pre>

rst_n <= 'ENABLE_N;</pre>

#(STEP*1/4)

#STEP

rst_n <= 'DISABLE_N;</pre>

#(STEP*12)

$finish;

end

always @(negedge clk) begin

$display("pc:%h inst:%h acc:%h", pcout, {opcode,operand}, dp2.accum);

$display("dmem:%h %h %h %h", dmem[0], dmem[1], dmem[2], dmem[3]);

end

endmodule

```

以前の演習での記述と同じく、周期 10nsec(=100MHz) のクロックを発生している。 命令メモリとデータメモリの初期設定を行っている。データメモリと同様に imem を 定義して、その初期値を以下の文で与えている。

```

$readmemb("imem.dat", imem);

```

命令は2進数の方が読みやすいと思い、2進数になっている。imem.dat を以下のように初期化してみよう。データファイルの中でも $_{-}$ とコメントは同様に用いることができる $^{3}$ 。

```

0001_00000000 // LD 0

0110_00000001 // ADD 1

1000_00000010 // ST 2

```

このメモリから読み出した命令は opcode と operand に分離され、operand はそのままデータメモリのアドレスに使われる。

```

assign {opcode, operand} = imem[pcout];

```

この書き方は格好いいのだが、サイズをまちがえると酷い目に合うので注意が必要である。

## 演習 3.4:

X,Y,W,Z が 0,1,2,3 番地に格納されているとする。(X-Z) AND (Y-W) を演算する命令コードを書き、実行して答えを確認せよ。なお、答えは accum 上に出た時点で終わりにして良い。

### 3.2.2 分岐命令の付加

次に分岐命令を取り付けてみよう。BEZ(1001) 命令ではアキュムレータが 0 の時、BNZ(1010) 命令では 0 でない時に、分岐条件が成立する。この信号を pcsel として図に表しているが、Verilog の記述ではこの信号名を使っていない。これは、always 文中の if 文中に、この程度の条件ならば簡単に書けるからである。条件が成立すれば、pc に operand を書き込みそれ以外は pc を 1 増やす。もちろん、rst\_n が 0 ならばそちらが優先されて pc は 0 になる。

```

'include "def.h"

module accum(

input clk, input rst_n,

input ['OPCODE_W-1:0] opcode,

```

<sup>&</sup>lt;sup>3</sup>実はちょっと問題があり、web を参照のこと

```

input ['ADDR_W-1:0] operand,

input ['DATA_W-1:0] ddatain,

output we,

output ['ADDR_W-1:0] pcout,

output ['DATA_W-1:0] accout);

reg ['DATA_W-1:0] accum;

reg ['ADDR_W-1:0] pc;

wire ['DATA_W-1:0] alu_y;

wire op_st, op_bez, op_bnz, op_addi ;

assign op_st = opcode == 'OP_ST;

assign op_bez = opcode == 'OP_BEZ;

assign op_bnz = opcode == 'OP_BNZ;

assign we = op_st;

assign accout = accum;

assign pcout = pc;

alu alu_1(.a(accum), .b(ddatain), .s(opcode['SEL_W-1:0]), .y(alu_y));

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) pc \ll 0;

else if (op_bez & (accum == 0) | op_bnz & (accum != 0))

pc <= operand;</pre>

else pc <= pc + 1;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) accum <= 0;</pre>

else if(!op_st & !op_bez & !op_bnz ) accum <= alu_y;</pre>

end

```

#### endmodule

ここでは、ALUを使った命令以外が3つに増えているため、これをそれぞれ識別して信号名を付けている。このように命令によって対応する信号を設けることをデコード (decode:解読) と呼ぶ。

```

assign op_st = opcode == 'OP_ST;

assign op_bez = opcode == 'OP_BEZ;

assign op_bnz = opcode == 'OP_BNZ;

```

命令をデコードすると、対応する信号の値によって所定の制御を行えば良いので記述がすっきりする。

実装した accum.v で、掛け算のプログラムを実行してみよう。imem.dat を下のように設定する。

```

0001_00000000 // LD 0

0110_00000001 // ADD 1

1000_00000000 // ST 0

0001_00000010 // LD 2

0111_00000011 // SUB 3

1000_00000010 // ST 2

1010_00000000 // BNZ 0

1001_00000111 // BEZ 7

```

このプログラムでは 1 番地と 2 番地の掛け算を行って 0 番地に書き込むため、dmem.dat は、例えば以下のようにしておけば、 $2 \times 3$  が計算されるはずだ。

0000

0002

0003

0001

テストベンチは以前の例題とほとんど同じなので省略する。

## 演習 3.5

1番地に X が格納されている。 X+(X-1)+...+1 を計算するプログラムをシミュレーションで実行せよ。

## 第4

# アキュムレータマシンの中身

## 4.1 抽象化のレベル

今まで、CPUの構成要素はブラックボックス化して扱い、その詳細に触れることはしなかった。ALUは計算をする所、レジスタはデータを格納する所など、その機能を中身を気にしないで理解してもらえば良かった。Verilogの記述もある意味で、抽象化された記述である。ブラックボックス化あるいはモデル化はシステムを理解する上で重要で、中身を完全に知ることはできないし、その必要もない。コンピュータは物理的には大規模な集積回路(LSI)チップで実現されるが、命令のレベルからチップまでには下に示す階層が存在する。

- 命令セットアーキテクチャ:命令がどのように動くかを決める。次の章でくわ しく紹介する。

- マイクロアーキテクチャ: CPU、メモリ、I/O が、どのタイミングでどのように 演算やデータのやりとりを行い、制御を行うかを、大雑把にモデル化したもの。

- RTL (Register Transfer Leve):マイクロアーキテクチャをさらに詳細化し、演算、 データのやりとりを詳細にモデル化したもの。

- ゲートレベル: RTL を実現するディジタル回路の論理ゲートの接続を示すレベル。

- 回路レベル:論理ゲートのトランジスタ接続を示すレベル。現在使われるトランジスタとは、CMOS (Complimentary Metal Oxide Semicondoctor) トランジスタであり、NMOSとPMOSという対称的な性質を持つ二種類のトランジスタを使って回路を構成する。

- レイアウトレベル:トランジスタを半導体チップ上に実装する方法。

今までは、マイクロアーキテクチャと RTL を中心に、命令セットアーキテクチャを理解しようと試みてきた。ここでは、きちんと命令セットアーキテクチャを紹介し、RISC の構造を説明する前に、下の階層であるゲートレベルについて触れる。この章は、コンピュータを下のレベルまで理解しなくても良い場合は、スキップしても良い。

## 4.2 それぞれのモジュール

## **4.2.1** ALU(Arithmetic Logical Unit)

ALUは、加算、減算、乗算、論理演算、シフト、比較など、データを処理するための様々な演算を行ってくれる装置である。

ALU は図 2.4 に示すように A, B 二つのデータ入力と制御入力 s があって、出力として Y がある。com の内容に応じて、A,B の入力に対して所定の演算を行って Y に出力するのが ALU の役目である。

図 4.1: ALU のモデル

ここでは、

| AND |

|-----|

| OR  |

| SL  |

| SR  |

| ADD |

| SUB |

|     |

を想定した。では、この ALU の中身がどうなっているかを知っておこう。

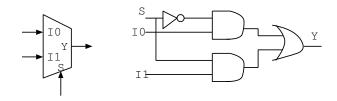

## マルチプレクサ

図 4.2: 2 入力マルチプレクサ

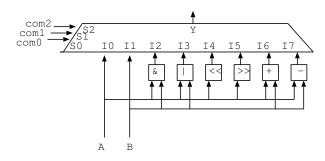

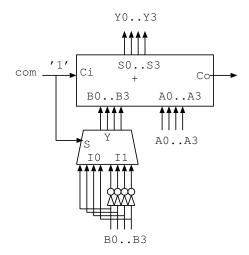

ALU は複数の演算を行う演算ユニットがあって、これを com の値によって切り替える機能を持つ。これは実はマルチプレクサ、あるいはデータセレクタと呼ばれるディジタル回路で実現される。2 入力のマルチプレクサを図 4.2 に示す。これは図中に示すゲートの組み合わせで簡単に実現できる。マルチプレクサは、ディジタル信号の切り替えスイッチで、S=0で入力 IOが、S=1で入力 II が Y に出力される。ゲートの図は面倒なので書かないが、4 入力のマルチプレクサ、8 入力マルチプレクサも想定できる。図 4.3 には 8 入力のマルチプレクサを用いて ALU を構成する方法を示す。

図 4.3: ALU の実現方式

このマルチプレクサという回路は、すごく簡単だが、実は CPU のデータパスを構成する上で鍵となる部品であり、後で繰り返し登場することになる。

## 4.2.2 加算器

図 2.3 中のそれぞれの演算に相当するモジュールのうち、AND や OR はそれぞれ AND ゲート、OR ゲートで構成できる。シフトは実は1ビットシフトならば、線の繋ぎ変えだけで良い。となるとやはりここで中心になるのは加算器ということになる。まずは、もっとも簡単な方法を説明しよう。

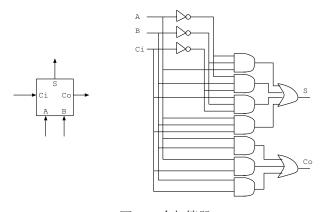

二進数のたし算を行うためには、下の桁から順に一桁ずつ足して行き、結果を上に繰り上げる。この繰り上がりのことをキャリ (Carry:桁上げ) と呼ぶ。

この例では一番上の段にキャリを示している。加算を実行するためには、それぞれの桁の入力を A, B, 下の桁からの入力を Ci とすると、以下の真理値表を実現すれば良い。

図 4.4: 全加算器

この論理回路も簡単なゲートの組み合わせで図 4.4 に示すように実現できる。これが 1 桁の全加算器 (full adder) である。n 桁の全加算器を作る場合、必要な桁分だけ並

べて、下の桁の Co を自分の Ci に、自分の Co を上の桁の Ci に接続して数珠繋ぎにする。これで、ちょうど手で計算する場合と同様に下のけたから桁上げ信号が伝搬して行って、加算ができる。一番下の桁 Ci 入力は使わないので Low レベルにして、0を入れる。この様子を図 4.5 に示す。キャリ信号がさざ波 (リプル) のように伝わって行くことからこの加算器をリプルキャリ加算器 (ripple carry adder) と呼ぶ。

図 4.5: リプルキャリ加算器

加算器は、ALU の中でもっとも複雑な構成要素なので、動作速度の足を引っ張ることが多い。リプルキャリアダーは、単純だが桁数分だけ遅延が積み重なるため、動作が遅く、よほど簡単な場合以外は使われない。キャリが発生するかだけを調べる先見回路を使うキャリ先見加算器 (Carry Look-ahead Adder)、アレイ状に部分加算器を並べるプリフィックス加算器 (Prefix Adder) などが実際の CPU では用いられる。

## 4.2.3 減算器

第2章で触れたが、減算を行うためには2の補数を加算すれば良く、2の補数を作るには以下の手順を踏めばよかった。

- 1と0を反転する。

- +1 する。

1と0の反転はNOT ゲートあるいはインバータと呼ばれる簡単な論理ゲートで実現できる。+1は加算器で可能だが、この目的だけで加算器を使うのはもったいないので、ちょっとトリックを使って、図4.6に示す回路でA-Bの減算器が構成可能である。ここでは、Bを反転してAと加算するが、この際、加算器の一番下の桁のキャリ入力をHレベルにして1を入れておく。このことで、A+(NOTB)+1が実現できる。加算器と減算器は多くの部分が共有可能なので、図2.3のように別モジュールにするのはバカバカしい。そこで、多くの場合、図4.7に示す加減算器を使う。

図の回路では、com が0 の時は、普通にB が入力されて加算器になる。1 の時は、NOT B が入力されると共に、もっとも下の桁の入力が1 になることで+1 が行われ、結果として減算器となる。

図 4.6: 減算器

図 4.7: 加減算器

#### 4.2.4 レジスタ

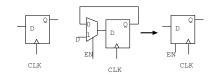

基本的にレジスタは Flip Flop(FF) から作る。FF は 1 ビットの記憶回路で、最も良く使われる D-FF は、図 4.8 に示す記号で表され、D 入力の値をクロックの立ち上がりに同期して記憶して Q に出力する。FF の内部構造はここでは深く触れないが、トランジスタを 12-14 個程度必要とするやや複雑な回路である。

3章で触れたように CPU を含めて多くのディジタル回路はクロックに同期して全回路が動作する同期式を用いている。この方式では、クロックの立ち上がりで、いつでも FF にデータがセットされることになり、使い難い。そこで、通常用いるのは、D-FF に Enable(イネーブル) 入力を付けた Enable 付き D-FF である。この FF は EN(Enable) 入力が 1 の時にのみ D 入力からデータを取り込み、0 の場合は、現在記憶しているデータをとっておく。この Enable 付き D-FF を必要なビット数分並べてクロックと EN 入力を共通化したものがレジスタである。レジスタは、EN 入力が 1 の時にクロックの立ち上がりに同期してデータを記憶する。

アキュムレータは、この Enable 付き Flip Flop で実現するが、2 章に示したアキュムレータではプログラムカウンタ PC は毎回 1 を足すので、Enable はなくても良い。

図 4.8: D-FF

レジスタよりも大量にデータを記憶させる素子がメモリであるが、これについては10章に紹介する。ここで使うメモリは、同期式のSRAM(Static Random Access Memory)である。半導体チップ内のメモリの多くはこの形を取る。

## 4.3 論理合成と論理圧縮

## 4.3.1 Verilog 記述とゲートレベル

Verilog 記述の一部は、対象とするハードウェアモジュールとそのまま対応する。例えば、図 4.2 に示すマルチプレクサは、以下の記述がそのまま対応する。

assign Y = S? I1: I0;

AND, OR などの論理演算はそれぞれ対応する論理ゲートに変換される。

assign Y = A & B; assign Y = A | B; 図 4.8 に示す D-FF は、Verilog 記述の以下に対応する。

always @(posedge CLK)

$if(EN) Q \ll D;$

しかし、Verilog の記述が常に一対一でゲートレベルの回路図に対応するのではない。

assign Y = A + B;

と書いた場合、これがどのような加算器に変換されるかは、論理合成用ツールとそれに与えるパラメータに依存する。論理合成用ツールは遅延時間に余裕があれば、コストの小さいリプルキャリ方式の加算器を生成し、高速な演算が要求されれば、プリフィックス方式の加算器を生成する。また、実は先に示したマルチプレクや論理演算の記述も場合によっては他の回路と共用されたりする関係で、違った形で論理合成される可能性がある。次にこの論理合成ツールについて解説する。

## 4.3.2 合成ツールと使い方

今までは、Verilog はハードウェア構造を記述し、シミュレーションするだけだった。しかし、記述されたハードウェアは何らかのデバイス上で実現しなければ意味がない。このためには Verilog 記述をゲート部ベルの接続図 (ネットリスト) に変換し、様々の最適化を行う作業が必要である。これを論理合成、圧縮と呼ぶ。今日はこの合成ツールの使い方を習得し、これを使って今まで設計してきた POCO を合成、圧縮することが目的である。

論理合成圧縮ツールは、プログラミング言語におけるコンパイラに相当するが、対象がハードウェアであるために、コンパイラよりもはるかに処理が複雑で、時間がかかり、また、ツール自体も高価である。現在、学生レベルで無料あるいは安価に使える論理合成圧縮ツールには以下のものがある。

- FPGA(Field Programmable Gate Array)、すなわち書き換え可能な大規模 LSI のベンダの提供する合成ツール。Xilinx 社の ise、Altera 社の Quartus II は、webパックと呼ばれる簡易版を無料で提供している。webパックは一部の機能が制限されているが、本書で記述するの回路ならば十分合成可能である。

- VDEC(VLSI Design and Education Center: http://www.vdec.u-tokyo.ac.jp/welcome.html) で、研究教育目的で安価で本格的な CAD を利用可能である。

- PARTHENON、このテキストで、以前、用いていた合成ツール。元々NTTが開発したが現在はNPO法人が管理し、独自の記述言語であるSFLのみを受け付け、Verilogは受け付けない。

ここで、論理合成、圧縮用のツールとその利用法については、本書中ではではこれ以上記述せず、web 上で以下の環境を提供することにする。論理合成圧縮用のツールはバージョンアップが激しく、対象となる LSI の進歩も急速である。本書中に詳細を記述してもあっという間に記述が古くなってしまうだろう。web 上に置けばその都度更新することで最新の利用法をサポートすることができる。現在利用可能なのは以下の環境である。

- Xlinix 社の WebPack を利用した環境。Windows/Linux の走る PC があれば無料で個人レベルでインストールして使うことができる。また、同社が販売している Spartan 3E 用のテストボード上で POCO を実装し、もぐらたたきやピンポンゲームなどを動かしてみることができる。

- VDEC により提供される Synposys 社の Design Compiler を用いた論理合成および圧縮。これは、ライセンスの利用を許可された大学や高等専門学校のみで実験ができる。計算センターや、研究室の指導教員に相談されたい。CAD ツールのみの演習は、オクラホマ大の開発したフリーのライブラリを用いて可能である。さらに進んで、富士通 e-shuttle 社のライブラリを用いて Synopsys 社の IC Compiler を利用して実際のチップを設計実装することができる。これも web 上で掲示しているので、利用のためには研究室の指導教員に相談されたい。

## 第5

# 汎用レジスタマシンへの拡張

## 5.1 汎用レジスタマシン

今までアキュムレータマシンの命令について検討してきた。3章で分岐命令を導入したことで、簡単なプログラムが書けるようになった。プログラムを書くことのできる命令の一揃いを命令セットと呼び、命令セットの作り方、あるいはその作り方に基づいて出来上がった命令セットのことを命令セットアーキテクチャと呼ぶ。命令セットアーキテクチャとは4章で紹介した抽象化の上のレベルに当たり、ハードウェアとソフトウェアのインタフェースである。ハードウェア設計者は、この命令セットアーキテクチャを実現するために様々な要求に応じて様々な構成を作ることができる。お金は掛かっても高速な CPU が欲しい場合と、遅くても良いので安くて電力消費が少ないものを作りたい場合では、構成は全く違ったものになる。しかし、同じ命令セットアーキテクチャを使っていれば、同じプログラムが動く。一方、プログラマは、どのようなハードウェアになっているのかを気にしないで、命令セットだけを知っていれば、プログラムを書くことができる。

この章では、より高度な命令セットアーキテクチャをもっとも簡単な実現モデル(マイクロアーキテクチャ)を示しながら紹介する。

さて、アキュムレータマシンは、ループを含むアルゴリズムの実行が可能であったが、以下の問題があった。

- アキュムレータだけしかレジスタがないので、演算の度に結果をメモリに格納 する必要がある。

- アキュムレータだけしかレジスタがないため、メモリのアドレスを動的に指し 示す機能がない。つまりポインタの実現ができない。

さらに、これはアキュムレータマシンの一般的な問題ではないのだが、アドレスの 指定が長くなりすぎると面倒なので、アドレス空間を4ビット、すなわち全体で16と した点にも問題がある。コンピュータの歴史を振り返ると、開発するプログラムサイズは年々増大し、必要とされるアドレス空間は直線的に増加している。現在の高性能のマイクロプロセッサが 64 ビットアーキテクチャを採用している主な原因は 32 ビットアーキテクチャではアドレス空間が不足するためである。このことを考えると、アドレス空間 4 ビットはいくら演習用でもちょっとひどすぎる。

そこで、以下の改造を行おう。

- レジスタ数を8個に増強する

- アドレスを 16bit に拡張して、アドレス空間を 64K とする

まず、8個のレジスタは、基本的に全てが同じ機能を持たせるようにする。初期のマシン(現在でも8ビットマシンなどは)ではレジスタの機能が専門化され、レジスタによって可能な演算や操作(メモリのアドレスのみ格納する等)が決っている場合が多かった。これを専用レジスタマシンと呼ぶ。しかし、専用レジスタマシンは、レジスタの機能を考えてプログラムをするのが大変で、コンパイラも作りにくい。このため、半導体の面積の余裕ができるにつれ、一部の例外を除いてすべてのレジスタが同様にすべての機能を実現できるマシン、すなわち汎用レジスタマシンに移行した。我々も汎用レジスタマシンを考えよう。

汎用レジスタマシンでは、レジスタが複数あるので、代表的な演算命令のオペランドが2または3となる。すなわち、2オペランド命令あるいは3オペランド命令となる。

ADD r0, r1 r0<-r0+r1

ADD r0, r1, r2 r0<-r1+r2

ここで、r0 は結果が格納されるレジスタであり、ディスティネーションレジスタ(オペランド)と呼ぶ。一方、r1(r2)は、元となるデータが格納され、演算によって変化しないレジスタであり、ソースレジスタ(オペランド)と呼ぶ。マシンによっては、オペランドに、アキュムレータマシン同様、メモリのアドレスを書くことができるものもある。

ADD r0, 1000 r0<-r0+(1000) ADD 1000, 2000, 2002 (1000)<-(2000)+(2002)

最初の命令はr0 と 1000 番地の中身を足して、答えをr0 に格納し、次の命令は2000 番地と2002 番地の中身を足して答えを1000 番地に格納する。

ここでは、ディスティネーションオペランドを一番左に書く表記法を採用している。この表記法は IBM や Intel のマシンで使われている方法で、現在一般的である(ディスティネーションオペランドを一番右に書くやり方もあり、DEC やモトローラのマシン、日立の SH などに使われている)。

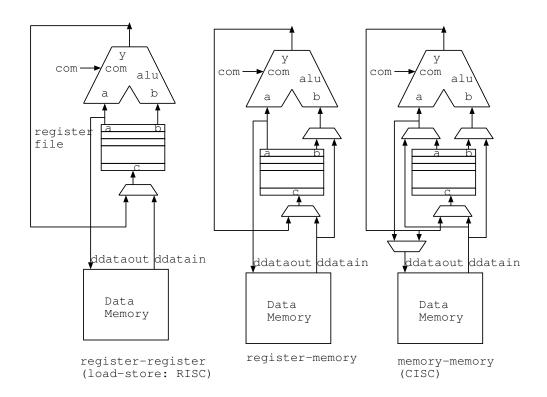

## 5.2 汎用レジスタマシンの分類

汎用レジスタマシンの命令セットは、演算命令のオペランドにメモリを指定できるかどうかによって以下のように分類される。

- まったく指定できない: register-register アーキテクチャ、load-store アーキテクチャまたは RISC(Reduced Instruction Set Computer) と呼ばれる。オペランドにメモリを指定できないため、演算を行う場合、必ずレジスタに値を Load してからレジスタ間で演算し、答えをメモリに Store する。一定の処理を行うための命令数は多くなるが、個々の命令は単純化され固定長で実装可能である。SPARC,MIPS,ARM,SH-4 などのマイクロプロセッサはこの命令形式を用いている。

- どこでも指定できる: memory-memory アーキテクチャ、オペランドのどの部分でもメモリが指定できる。もちろんレジスタ間でも演算が可能だが、メモリ中のデータ同士を直接計算する場合が多くなる。一定の処理を行うための命令数は少ないが、個々の命令は可変長にする必要があり、複雑になるため CISC(Comptex Instruction Set Computer) と呼ばれる。DEC の VAX-11 で用いられ、80 年代はメジャーであったが、性能向上が難しいことから現在はほとんど使われていない。

- 1つだけ指定できる: register-memory アーキテクチャ、オペランドに一ヶ所だけ メモリを指定できる。多くの場合 2 オペランド命令でソースオペランドに限ら れる。register-register 型と memory-memory 型の中間的な性質を持つ。一定の処 理を行うための命令数はさほど多くならず、命令は可変長にする必要があるが、 memory-memory 型ほど悲惨なことにはならない。現在、デスクトップやラップ トップで最も良く用いられている Intel/AMD の IA32,IA64 はこの型に属する。

例えば 0x1000 番地のデータと 0x1010 番地の内容を加算して 0x2000 に格納する場合、register-register 型では以下のようになる。

**0x1000** の中身をレジスタに持ってくる **(LD) 0x1010** の中身を別のレジスタに持ってくる **(LD)** 加算

0x2000 に答えを格納 (ST)

このように register-register 型は、命令数が多いことがわかる。しかし、メモリのアドレスは LD,ST のみで済み、命令長を固定にすることが可能である。 一方、memory-memory 型では一命令ですむ。

0x1000 の中身と 0x1010 の中身を足して 0x2000 に格納

図 5.1: 汎用レジスタマシンのデータパス

しかし、オペランドにはレジスタも指定できるので、命令長は長くなったり短くしたりしなければならないことがわかる。

register-memory 型は、ディスティネーションは、レジスタのみ許される場合が多いので以下のようになる。

0x1000 の中身をレジスタに持ってくる (LD)

0x1010 の中身を加算

0x2000 に格納 (ST)

これも、ADD 命令にメモリアドレスを書く場合と書かない場合で、命令長を変える必要があるが、その可変の程度は memory-memory 型よりもひどくはない。一方、一命令では済まず、3 命令必要になっている。

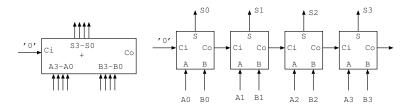

3つの方式のハードウェア構成を考えてみよう。複数の汎用レジスタは、レジスタファイルというハードウェアモジュールで実装される。レジスタファイルは小規模なマルチポートメモリであり、ここでは図5.1に示すように、読み出しに2ポート(a,b)、書き込みに1ポート(c)を持っている。今、レジスタファイルの中に8個のレジスタが入っているとすると、好きな番号のレジスタをaポート、bポートから独立に読み出すことができる。同時に、cポートからデータを書き込むことができる。

これを単純にアキュムレータの代わりに入れ替えた構成が、図の真ん中に示す register-memory 型である。この点で、register-memory 型はアキュムレータマシンのもっとも自然な発展であると言える。次に左に示す register-register 型は、メモリから ALU への直接入力が存在せず、全てのデータが一度レジスタを介して演算される。一方で、memory-memory 型はレジスタとメモリが同様に ALU に接続されている構成である。

さて、register-memory 型は、アキュムレータマシンの自然の発展であり、また、最も良く用いられている Intel/AMD の CPU の命令セットは、この形である。しかし、この型が最もうまく行っていると勘違いしてはならない。実は Intel/AMD のマイクロプロセッサは、Pentium II 以降は、register-memory 型の命令を内部的に register-register型に変換して実行している。register-memory 型の見掛けを維持しているのは、アキュムレータマシンの自然な発展として register-memory 型を採用してしまったが故に蓄積したプログラムとの互換性 (Compativility) を保持するために過ぎない。高速に実行するという点でいうと、register-register型つまり RISC はとことん優れており、わざわざ実行時に変換して実行せざるを得ないのだ。つまり、これらのプロセッサは外面が register-memory 型でも、一皮剥けば RISC であり、組み込み用ではほとんどの CPUが RISC であることを考えると、プロセッサの命令セットという点では RISC の圧勝である。

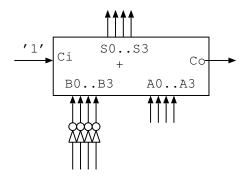

そこで、ここでも、今までのアキュムレータマシンを register-register 型、すなわち RISC に拡張していくことにする。ここで、この RISC に名前を付け、POCO と呼ぶことにする。

## 5.3 16bit RISC: POCO

POCO の基本構成を以下のように決める。

- 命令メモリ:16bit ×アドレス 16bit=アドレス空間 64K

- データメモリ:16bit ×アドレス 16bit=アドレス空間 64K

- レジスタ:16 本 (全部 16bit):r0-r7

- 機械語命令:16bit 固定長

これは、小規模な組み込み CPU としてはそこそこリアルな構成である。

### 5.3.1 メモリの読み書きをどうするか?

まずもっとも問題となるのはメモリの読み書きである。メモリのアドレスを 16bit に拡張したため、LD 命令と ST 命令で直接アドレス指定すると、命令の全体長を越えてしまう。また、ポインタや配列の実現ができないなどのアキュムレータマシンの問題点を解決できない。

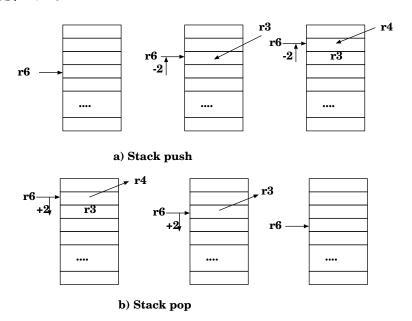

そこで、POCOでは他のRISCと同じくレジスタの中身で、メモリのアドレスを表す方法を採用する。これをレジスタ間接メモリアクセスと呼ぶ。

### LD r0, (r1) r0 < -(r1)

上記の命令を実行すると、r1 に中身がアドレスとなり、読み出されたデータが r0 に格納される。r1 が 0 ならば 0 番地、100 ならば 100 番地が読み出される。r0-r7 には 16 ビットの数が格納されるので、全アドレス空間をアクセスすることができる。この場合、r1 はポインタそのものであり、この値に演算を行うことで配列、スタックなどのデータ構造を実現することができる。

STも同様に表される。

## ST r0, (r1) r0 -> (r1)

この場合、r0 の中身が、r1 で指定するアドレスに書き込まれる。すなわち、r1 が 0 ならば 0 番地、100 ならば 100 番地に r0 の中身が書き込まれることになる。ここで、データの移動の方向が ST 命令のみは左(レジスタ)から右 (メモリ)になる点に注意されたい。

## 5.3.2 基本演算命令

次に、基本的な演算命令はレジスタ同士の演算である。

今回、ALU についてはビット幅が 16 ビットになっただけで、アキュムレータマシンと同様の機能を想定する。この場合以下の命令が定義できる。

AND r0, r1  $r0 \leftarrow r0$  and r1 OR r1, r2  $r1 \leftarrow r1$  or r2 SL r0  $r0 \leftarrow r0 \ll 1$  SR r2  $r2 \leftarrow r2 \gg 1$

さて、POCO は RISC すなわち register-register 型なので、演算はレジスタ同士でしか許していない。ところが、ここで問題があることに気づく。メモリからのデータがレジスタ間接指定で、演算がレジスタ同士でしか許されないのならば、レジスタにアクセスする番地を入れることができないではないか?最初にレジスタに値を設定する手段を設けておかないと、メモリからデータを取ってくることができなくなってしまう。これでは困る。そこで、命令中に直接数字を指定する命令を用意する。これがイミーディエイト命令である。

#### LDI r1,#3 r1 <- 3

これは、r1に3という数値を直接入れてしまう命令である。メモリの番地を指定しているのではなく、あくまで3という数自体を入れていることに注意されたい。この指定方式を直値(即値)指定あるいはイミーディエイト(Immediate)指定と呼び、この指定を使った命令を直値命令あるいはイミーディエイト命令と呼ぶ。同様に、演算についてもこの考え方を用いて、

#### ADDI r2,#5 r2 < -r2 + 5

とできると便利である。命令のオペランドが直接レジスタに入ったり、演算に使われたりするのは、やや特殊なケースと言って良い。このため、アセンブラ表記ではこのことを強調するために、イミーディエイトデータの前に#を付けて表すのが普通である。

ここでさらに一つ問題がある。このイミーディエイトデータを指定する領域を命令内に確保しなければならないが、命令は全体で16ビットに納めなければならない。この中にはオプコードが最低5ビット(32命令分)は必要であるし、レジスタを指定する3ビット(r0-r7で8つ分)も必要である。したがって、イミーディエイトデータ

に使える分は8ビットしかない。そこで、8ビットのデータを16ビットに幅を広げる手段が必要である。ここで2章で紹介した符号拡張が登場する。POCO内で使う符号付き数は、通常のコンピュータと同じく2の補数表現であらわす。そこで、符号を考えて拡張してやるのが原則である。しかし一方、符号を考えない数も扱う必要があるため、イミーディエイト命令は符号付きと符号無しの両方を用意する必要がある。

POCOでは以下の4つを用意する。

LDI rd,#X Load Immediate rd <- X (符号拡張)

LDIU rd,#X Load Immediate Unsigned rd <- X (符号拡張なし)

ADDI rd,#X ADD Immediate rd <- rd + X (符号拡張なし)

ADDIU rd,#X ADD Immediate Unsigned rd <- rd + X (符号拡張なし)

SUBI は用意する必要はない。これは、

#### ADDI r1, #-1

が可能であるからだ。他の演算も重要度はさほど高くないので、イミーディエイト命令としてはこれだけで良いだろう。ちなみに、イミーディエイトフィールドを 8bit にする、という選択は、「命令の長さが足りないから」という理由だけでなく、「16bit 全部持たせると無駄だから」という点からも合理的である。プログラムを書いてみると多くの場合、イミーディエイト命令では、1(あるいは 2 とか 3 とか小さな数)を足すとか引くとかが多く、意味のある桁数はさほど長くない。このような場合、全部持たせるというのは命令セットの設計上無駄が大きくなってしまう。

以上で基本的な演算が可能になる。例えば 0 番地の内容と 1 番地の内容を加算して 2 番地に格納するプログラムは以下のようになる。

LDIU r0,#0

LD r1, (r0)

ADDIU r0,#1

LD r2,(r0)

ADD r1,r2

ADDIU r0,#1

ST r1, (r0)

この場合アドレスが小さいので、LDIU、ADDIU は LDI、ADDI と同じである。ここでは r0 をポインタとして 1 ずつ進める方式を取っているが、その都度値をじかに LDIU 命令で設定しても良い。実はここまでのイミーディエイト指定では、下位 8bit しか指定されず、上位 8bit は符号ビットか 0 になってしまう。このため、16bit レジスタの上位 8bit に値を設定することができず不便だが、これに対処する命令 LHI(Load High Immediate) は、演習で実装しよう。

## 5.3.3 命令フィールドの設計

他の RISC 同様、POCO では 16bit 固定長に全命令を実現する必要がある。まず、オプコードを 5bit とする。これだと 32 命令実現可能である。32 はいくら教育用といえ、少なすぎるような気がするが、後で RISC 共通の方法を使って拡張する。

イミーディエイト命令は、レジスタを1つ指定する必要があるので、オプコードの後は、そのレジスタの番号を入れて残りをイミーディエイトデータに割り当てて、以下のようにする。

| LDI rd,#X   | 01000 ddd XXXXXXXX | rd <- X (符号拡張)        |

|-------------|--------------------|-----------------------|

| LDIU rd,#X  | 01001 ddd XXXXXXXX | rd <- X (符号拡張なし)      |

| ADDI rd,#X  | 01100 ddd XXXXXXXX | rd <- rd + X (符号拡張)   |

| ADDIU rd,#X | 01101 ddd XXXXXXXX | rd <- rd + X (符号拡張なし) |

例えば

ADDI r5,#100 01100 101 01100100

となる。

このようにオプコード(opcode: 01100), レジスタ (ddd)、イミーディエイト(XXXXXXXXX)など、命令中のそれぞれ意味を持った部分のことを命令フィールドと呼ぶ。

次に ADD などレジスタを 2 つ指定するタイプの命令について考えよう。同様に opcode は 5 ビットとし、レジスタ二つを指定するフィールドを設けると、残りは、 16-5-3\*2=5bit 余る。ここで、この余りのフィールドを用いて命令数を増やすことを 考える。すまわち、全ての ALU を用いた命令は、opcode を 00000 とし、この余りの 5 ビットのうち下位 3 ビットを ALU のコマンドに入れて演算を指定する。この下位 5 ビットを function(funct) フィールドと呼ぶ。3bit 目、4bit 目の 2 ビットが完全に余るが、これは将来のために取っておくことにし、ALU 命令ではここを 00 とする。すな わち、opcode が 00000 で、function が 00XXX であれば、ALU 命令であり、XXX が ALU のコマンドとなる。

今までと同じ ALU を利用すれば以下の命令が定義される。

| NOP |       |                 | 00000 |     |     | 00000 |

|-----|-------|-----------------|-------|-----|-----|-------|

| MV  | rd,rs | rd <- rs        | 00000 | ddd | sss | 00001 |

| AND | rd,rs | rd <- rd AND rs | 00000 | ddd | sss | 00010 |

| OR  | rd,rs | rd <- rd OR rs  | 00000 | ddd | sss | 00011 |

| SL  | rd    | rd <- rd<<1     | 00000 | ddd |     | 00100 |

| SR  | rd    | rd <- rd>>1     | 00000 | ddd |     | 00101 |

| ADD | rd,rs | rd <- rd + rs   | 00000 | ddd | sss | 00110 |

| SUB | rd,rs | rd <- rd - rs   | 00000 | ddd | SSS | 00111 |

ddd 同様、sss にはソースレジスタ rs を示す番号 (r0-r7:000-111) が入る。RISC では 先の図 5.1 に示すように、ALU の B 入力につながっているのはレジスタファイルの B ポートなので、ALU のコマンド 001: THB は、LD ではなくレジスタ間の転送命令で ある MV(move) となる点に注意されたい。THA は、今まで同様に NOP(No-operation) 命令となり何も行われない。この方法はなんだかセコいようだが、命令数を増やし、ハードウェアを簡単にするのに有効なので、ほとんどの RISC で同様の方法を用いている。

それでは LD, ST 命令を ALU 命令と同じ形で表現することにしよう。ここでは function の 5,4 ビット目が 01 で LD, ST を表すこととした。ST を先に持ってきたの はアキュムレータマシンと命令コードを同じにした方が慣れていていいかと思ったためで、深い意味はない。aaa はメモリアドレスを示すレジスタという意味で、やはり r0-r7 までのレジスタ番号が入り 000-111 で表す。

ST rs, (ra) rs -> (ra) 00000 sss aaa 01000 LD rd, (ra) rd <- (ra) 00000 ddd aaa 01001

#### 演習 5.1

0番地,1番地にそれぞれ A,B が格納されている。(A-B) OR B の演算を行い、2番地に答えを格納するプログラムをアセンブラ表記、機械語の両方で示せ。

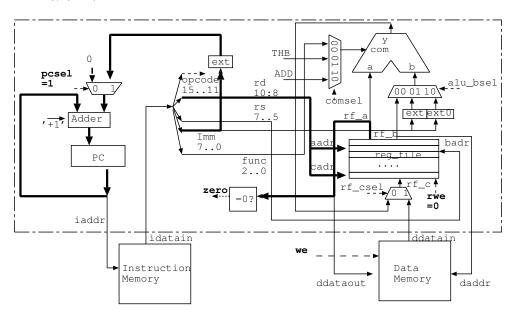

## 5.4 POCO の内部構造

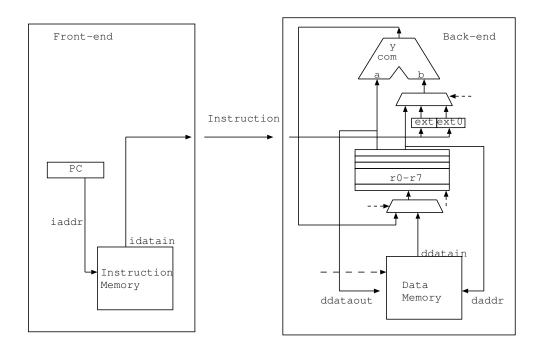

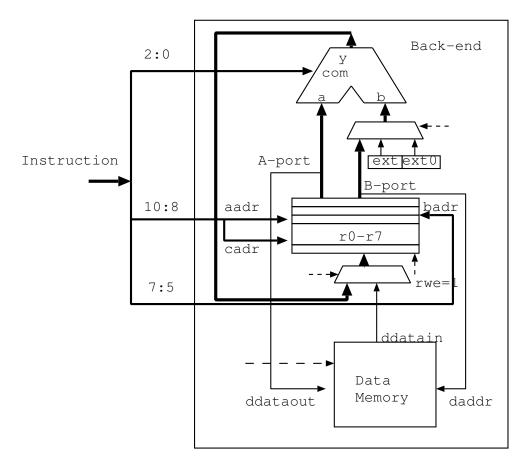

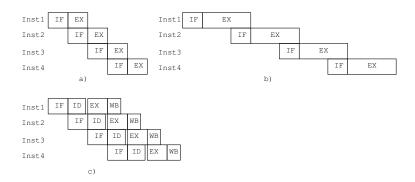

アキュムレータマシンと同じく、POCO のデータパスは、大きく分けて、命令を命令メモリから取ってくる部分(フロントエンドと呼ぶ)取ってきた命令に基づいて演算やメモリアクセスを行う(バックエンドと呼ぶ)に分けることができる。図 5.2 に 概略図を示す。

フロントエンドでは PC(Program Counter) の指し示すアドレスに格納されている命令を読み出す。読み出された命令は idatain からバックエンドに送られる。PC は次の命令を読み出すためにカウントアップされる。

### 5.4.1 レジスタ間演算命令の実行

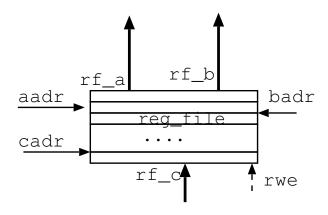

次にバックエンドに目を向けよう。バックエンドの主な構成要素は、r0-r7 までのレジスタがまとめて格納されているレジスタファイルと演算を行う ALU、データメモリであり、データの流れを切り替えるためにマルチプレクサが配置されている。レジスタファイルは図 5.3 に示す 3 ポート構造を想定する(現時点では、実は読み出しのaポートアドレスと書き込みのcポートアドレスは共有可能である)。レジスタファイ

図 5.2: データパスの概略図

ルは一種のメモリであり、aadr から与えられた番号(3 ビット)のレジスタが内容が rf\_a に読み出され、badr に与えられた番号(3 ビット)のレジスタの内容が rf\_b に読み出される。一方、書き込みについては、cadr に与えた番号のレジスタに対して、rwe が 1 の時のクロックの立ち上がりで、rf\_c からのデータが書き込まれる。aadr, badr, cadr は後で解説するように命令中のレジスタを表すフィールドにより指定する。

図 5.3: レジスタファイル

POCO は、register-register マシンなので、メモリから ALU への直接パスは存在しない。メモリから読み出したデータは、マルチプレクサを介してレジスタファイルのrf\_c から書き込まれる。

まずは、レジスタ同士の演算命令を実行する場合を考える。

レジスタ同士の演算の機械語フォーマットは以下の通りである。まず opcode は 00000 で、これに続く 3 ビット (10 から 8 ビット) でディスティネーションレジスタを、次の 3 ビット (7 から 5 ビット) でソースレジスタを、最後の function5 ビット (4 から 0 ビット) で命令の種類を表す。

例えば、ADD r0,r1 を例に取ると、この命令の機械語は、以下のフォーマットになっている。

### ADD r0,r1 00000 000 001 00110

10 から 8 ビット目のディスティネーションレジスタ番号をレジスタファイルの A ポートアドレス (addra) に繋いで、ディスティネーションレジスタを A ポートから読み出す。7 から 5 ビット目のソースレジスタ番号の方は B ポートアドレス (addrb) に繋いで、ソースレジスタを B ポートから読み出す。ALU の入力用マルチプレクサの制御入力 alu\_bsel は 00 として、レジスタファイルからの値を入力してやる。

ALU で行う演算の種類は com で指定する。POCO の命令コードは、最後の funct コードの下 3 ビットが、com と一致するようになっている。つまり、110 ならば加算

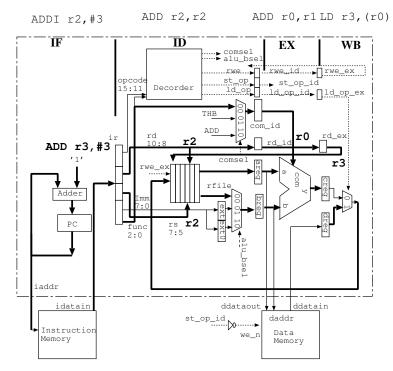

が行われる。先に述べたように、この方法はセコいようだが、単に繋げば良いため楽なことがわかる。ディスティネーションレジスタとソースレジスタ間の演算結果は、レジスタファイルに書き込まれる。このため、Cポートのアドレスには、ディスティネーションレジスタ番号を入れ、レジスタファイル書き込み用マルチプレクサの制御線rf\_cselを0にする。書き込み制御信号rwe=1とすればレジスタファイルへの書き込みが行われる。上記のデータの流れについて図5.4に示す。

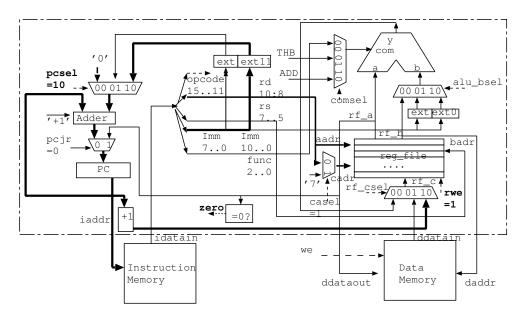

図 5.4: レジスタ間演算命令の動き

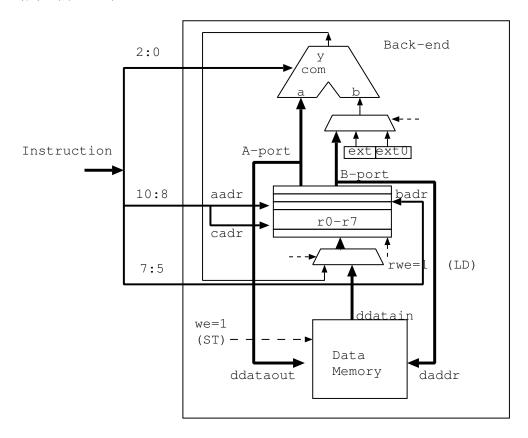

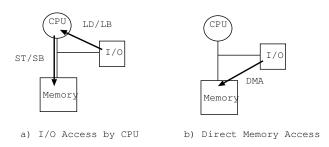

# 5.4.2 LD/ST 命令の実行

LD命令、ST命令の場合、メモリのアドレスを格納しているレジスタは、ソースレジスタとして8-6 ビット目に指定されている。Aポートの出力は、直接データメモリのアドレスに接続しているので、レジスタから値を読み出せば自動的にアドレスが与えられる。LD命令の場合、読み出されたデータは、ALUからの演算結果に代わってCポートで与えられたディスティネーションレジスタに格納される。このため、レジスタファイルの書き込み用マルチプレクサの制御線rf\_cselを1とする。一方、Bポートの出力は直接データメモリの入力データに接続されているので、ST命令が実行される場合、ソースレジスタの中身が書き込まれる。この場合はデータメモリの書き込み制御線(we)を1にし、レジスタファイルの書き込み制御線(rwe)を0にする。この様子を図5.5に示す。

図 5.5: LD/ST 命令の動き

### 5.4.3 イミーディエイト命令の実行

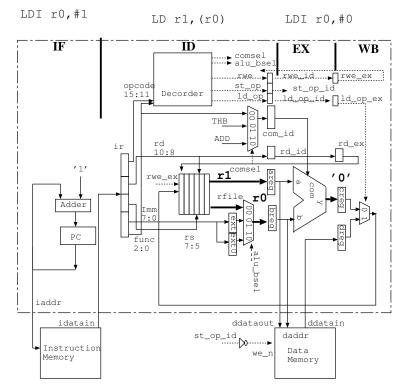

イミーディエイト命令は、ソースレジスタの指定がなく、下位8ビットがコード中に指定されている。例を以下に示す。命令はopcodeにより判定する。

LDI r0,#-32 01000 000 11100000 LDIU r0,#224 01001 000 11100000 ADDI r0,#-32 01100 000 11100000 ADDIU r0,#224 01101 000 11100000

ここで、機械語中の8 ビットを16 ビットのレジスタ中のデータと演算する際にビットの長さを揃えて16 ビットにする必要がある。この際に、符号を考えて16 ビット化する、すなわち符号拡張する方式と0を埋めて16 ビット化する0 拡張する方式がある。例えば ADDI は前者なので、0xffe0 すなわち-32 が r0 に加算され、ADDIU は後者なので0x00e0 すなわち 224 が加算される。

この命令を実行するには、まず機械語の下 8 ビットを ALU の B 入力まで引っ張って来る必要がある。引っ張ってきた結果は、符号拡張 (ext) あるいはゼロ拡張 (ext0) されて入力される。ちなみに ext, ext0 は、図中では箱で表しているが、実際は最上位ビットや 0 を並べて出力するだけで、非常に簡単なハードウェアである。ALU の B 入力選択用のマルチプレクサの制御入力は符号拡張の場合は 01、ゼロ拡張の場合は 10 にしてやる。

さて、イミーディエイト命令は直接 B 入力のデータを書き込むこと (LDI, LDIU) と 加算する (ADDI, ADDIU) だけなので、これを直接 ALU の com に入れてやる。ALU コマンド選択用のマルチプレクサ制御入力 comsel を命令に応じて切り替える。レジスタファイルへの書き込みは、レジスタ同士の演算命令と同じである。この様子を図 5.6 に示す。

# 5.4.4 制御回路

今までの解説で、各部のデータの流れはご理解いただけたと思う。この流れを実現するように、命令の種類に応じて制御信号を設定してやればそれぞれの命令を動作させることができる。制御する対象は ALU のコマンド入力を選択する comsel、ALU のB入力の選択用 alu\_bsel、レジスタファイルの書き込みを選択する rf\_csel で、これらはマルチプレクサの制御信号である。マルチプレクサの制御信号は、何が選択されても構わない場合があり、このような時はドントケアとなる。一方、レジスタファイルの書き込み信号 rwe とメモリの書き込み信号 we は、書き込む際は1にするが、その他の場合は0にしておかなければならない。レジスタやメモリはデータを取っておく

図 5.6: イミーディエイト命令の動き

のが役目なので、書き込み信号がドントケアということはあり得ず、書く場合以外には0にしておかなければならない。表 5.1 にそれぞれの命令に対する制御信号を示す。

| 表 3.1: 合命令の制御信方 |        |          |         |    |     |  |

|-----------------|--------|----------|---------|----|-----|--|

|                 | comsel | alu_bsel | rf_csel | we | rwe |  |

| ADDI            | 10     | 01       | 0       | 0  | 1   |  |

| LDUI            | 01     | 10       | 0       | 0  | 1   |  |

| SUB             | 00     | 00       | 0       | 0  | 1   |  |

| LD              | 00     | -        | 1       | 0  | 1   |  |

| ST              | _      | -        | -       | 1  | 0   |  |

表 5.1: 各命令の制御信号

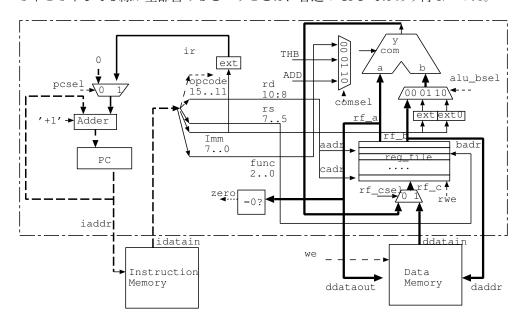

最後に今までの POCO のデータパスの全体図を示す。線がごちゃごちゃしている 印象を受けるかもしれないが、これでも CPU としては単純な部類に入る。実際、ごちゃごちゃしても線が全部書けるということは、普通の CPU ではあり得ないのだ。

図 5.7: POCO のデータパス

# 演習 5.2

ADDUI, LDI を表に付け加えよ。

# 5.4.5 POCOの Verilog 記述

# レジスタファイルの Verilog 記述

最初に図 5.3 のレジスタファイルの Verilog 記述は以下のようになる。

```

'include "def.h"

module rfile (

input clk,

input ['REG_W-1:0] aadr, badr, cadr,

output ['DATA_W-1:0] a, b,

input ['DATA_W-1:0] c,

input we);

reg ['DATA_W-1:0] r0, r1, r2, r3, r4, r5, r6, r7;

assign a = aadr == 0 ? r0:

aadr == 1 ? r1:

aadr == 2 ? r2:

aadr == 3 ? r3:

aadr == 4 ? r4:

aadr == 5 ? r5:

aadr == 6 ? r6: r7;

assign b = badr == 0 ? r0:

badr == 1 ? r1:

badr == 2 ? r2:

badr == 3 ? r3:

badr == 4 ? r4:

badr == 5 ? r5:

badr == 6 ? r6: r7;

always @(posedge clk) begin

if(we)

case(cadr)

0: r0 <= c;

1: r1 <= c;

2: r2 <= c;

3: r3 <= c;

4: r4 <= c;

5: r5 <= c;

```

6: r6 <= c;

default: r7 <= c;</pre>

endcase end

#### endmodule

この書き方はレジスタを個別に宣言していて、あまり賢いやり方ではない。

#### reg ['DATA\_W-1:0] r[0:7];

とメモリの形で宣言すれば、もっとずっと楽である。なぜわざわざ個別に宣言したかというと、メモリの形で宣言すると後で gtkwave でシミュレーションをする際に中身を見ることができなくなってしまうためである。通常、メモリは膨大なので、波形シミュレータでその中身をいちいち表示することはしない。そうは言っても演習時にレジスタが見えないと困るので、今回はこのようにした。あくまで演習用と考えて欲しい。

ここで always 文の中で if 文と case 文を使っている。case 文は、括弧内に示した信号について、そのデータに応じた処理をコロン:以降に書くことができる。どれも当てはまらない場合は、default:以降が実行される。大変見やすくて便利な文だが、if文と同じく、always 文でレジスタを記述する場合およびその他の特殊な構文中でしか使えない。

we が1である時に、書き込みを行う cadr の値に応じて入力 c がそれぞれのレジスタに書き込まれる。もちろん書き込みが行われるのはクロックの立ち上がりに同期している。case 文は便利だが、特殊な構文中だけしか使えないため、読み出しの部分では、?:のマルチプレクサ構文を使っている。

#### POCO 本体の Verilog 記述

さて、このレジスタファイルを使って、図 5.7 を比較的そのまま Verilog で記述したものを示す。まず、以下のように定義をしておく。

- 'define DATA\_W 16

- 'define SEL\_W 3

- 'define REG 8

- 'define REG\_W 3

- 'define OPCODE\_W 5

- 'define IMM\_W 8

- 'define DEPTH 65536

- 'define ENABLE 1'b1

```

'define DISABLE 1'b0

'define ENABLE_N 1'b0

'define DISABLE_N 1'b1

'define OP_REG 'OPCODE_W'b00000

'define OP_BEZ 'OPCODE_W'b10000

'define OP_BNZ 'OPCODE_W'b10001

'define OP_LDI 'OPCODE_W'b01000

'define OP_LDIU 'OPCODE_W'b01001

'define OP_ADDI 'OPCODE_W'b01100

'define OP_ADDIU 'OPCODE_W'b01101

'define F_ST 'OPCODE_W'b01000

'define F_LD 'OPCODE_W'b01001

'include "def.h"

module poco(

input clk, rst_n,

input ['DATA_W-1:0] idatain,

input ['DATA_W-1:0] ddatain,

output ['DATA_W-1:0] iaddr, daddr,

output ['DATA_W-1:0] ddataout,

output we);

reg ['DATA_W-1:0] pc;

wire ['DATA_W-1:0] rf_a, rf_b, rf_c;

wire ['DATA_W-1:0] alu_b, alu_y;

wire ['OPCODE_W-1:0] opcode;

wire ['OPCODE_W-1:0] func;

wire ['REG_W-1:0] rs, rd;

wire ['SEL_W-1:0] com;

wire ['IMM_W-1:0] imm;

wire rwe;

wire st_op, addi_op, ld_op, alu_op;

wire ldi_op, ldiu_op, addiu_op;

assign ddataout = rf_a;

assign iaddr = pc;

assign daddr = rf_b;

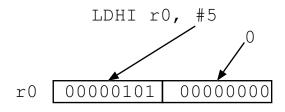

assign {opcode, rd, rs, func} = idatain;

```

```

assign imm = idatain['IMM_W-1:0];

// Decorder

assign st_op = (opcode == 'OP_REG) & (func == 'F_ST);

assign ld_op = (opcode == 'OP_REG) & (func == 'F_LD);

assign alu_op = (opcode == 'OP_REG) & (func[4:3] == 2'b00);

assign ldi_op = (opcode == 'OP_LDI);

assign ldiu_op = (opcode == 'OP_LDIU);

assign addi_op = (opcode == 'OP_ADDI);

assign addiu_op = (opcode == 'OP_ADDIU);

assign we = st_op;

assign alu_b = (addi_op | ldi_op) ? {{8{imm[7]}},imm} :

(addiu_op | ldiu_op) ? {8'b0,imm} : rf_b;

assign com = (addi_op | addiu_op ) ? 'ALU_ADD:

(ldi_op | ldiu_op ) ? 'ALU_THB: func['SEL_W-1:0];

assign rf_c = ld_op ? ddatain : alu_y;

assign rwe = ld_op | alu_op | ldi_op | ldiu_op | addi_op | addiu_op ;

alu alu_1(.a(rf_a), .b(alu_b), .s(com), .y(alu_y));

rfile rfile_1(.clk(clk), .a(rf_a), .aadr(rd), .b(rf_b), .badr(rs),

.c(rf_c), .cadr(rd), .we(rwe));

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) pc <= 0;

else

pc \le pc+1;

end

```

## endmodule

アキュムレータマシンと同じく、POCO は、クロック、リセットおよび命令メモリに対するアドレス iaddr、データ入力 idatain、データメモリに対するアドレス daddr、データ入力 ddatain、データ出力 ddataout、書き込み制御信号 we を入出力として持つ。

ddataout はレジスタファイルの a 出力が、daddr には b 出力が接続され、iaddr には pc が接続される。これらはもう決っているので最初に宣言する。

```

assign ddataout = rf_a;

assign iaddr = pc;

assign daddr = rf_b;

```

さて、命令メモリから読んで来た idatain を命令コード (opcode)、ディスティネーションレジスタ番号 (rd)、ソースレジスタ番号 (rs)、ファンクションフィールド (func) に分離する。

```

assign {opcode, rd, rs, func} = idatain;

```

この書き方は、複数の信号線をくっつけて束にする連結演算子,を左辺に使っていて格好良い書き方であり、下の書き方をまとめたものとなる。

```

assign opcode = idatain[15:11];

assign rd = idatain[10:8];

assign rs = idatain[8:5];

assign func = idatain[4:0];

```

このまとめた書き方は、行数が少なく、読んで分かりやすい。しかし、ビット幅がうまく合っていないと、誤った信号に分離されてしまっても、バグに気づき難い欠点もあるので利用時は注意が必要である。<sup>1</sup>

イミーディエイト命令時は、下位8ビットをイミーディエイト値として使うため、 これも分離しておく。

```

assign imm = idatain['IMM_W-1:0];

```

もちろん、imm は fs,func と物理的には同じなのだが、意味が違うため、違った信号名にしておく。

次に opcode で命令を判別する。これが以下の部分で、これをデコーダ (解読器) と呼ぶ。デコードの結果、命令の種類毎に信号線を用意した。これで、表 5.1 の信号を簡単に発生できる。

#### // Decorder

```

assign st_op = (opcode == 'OP_REG) & (func == 'F_ST);

assign ld_op = (opcode == 'OP_REG) & (func == 'F_LD);

assign alu_op = (opcode == 'OP_REG) & (func[4:3] == 2'b00);

```

$<sup>^1</sup>$ Verilog はシミュレーション時に左右のビット幅が合っていなくても実行されてしまい場合によっては気づかない。しかし論理合成時には Warning が出るので、この時にちゃんと見ていれば気づく

```

assign ldi_op = (opcode == 'OP_LDI);

assign ldiu_op = (opcode == 'OP_LDIU);

assign addi_op = (opcode == 'OP_ADDI);

assign addiu_op = (opcode == 'OP_ADDIU);

```

デコードしておけば、例えば ST 命令実行時にはデータメモリの書き込み信号を 1 にするという記述を以下のように簡単に記述できる。

#### assign we = st\_op;

さて、次は ALU 周辺のマルチプレクサを記述する。alu\_b は ALU の B 入力、com はコマンド入力である。A 入力は直接レジスタファイルの出力が繋がるのでマルチプレクサを記述する必要はない。

```

assign alu_b = (addi_op | ldi_op) ? {{8{imm[7]}},imm} :

(addiu_op | ldiu_op) ? {8'b0,imm} : rf_b;

```

以前から使っているように、Verilogではマルチプレクサを?:で表す。表 5.1 の制御信号との対応に注目されたい。3 入力以上のマルチプレクサは?を2回使って条件を順番にチェックしている。

ここで、まず分かり難い記述は、ALUのB入力であろう。ここでは、ADDIとLDIの実行時には符号拡張した値を選択する。

Verilog では 8bit の imm を 16bit に符号拡張する場合、

#### {{8{imm[7]}},imm}

と記述する。まず imm の最上位ビットつまり 7bit 目を切り出す (imm[7])。次にこれを 8 個分並べる。これを Verilog では

#### {8{imm[7]}

と書くことができる。これは

```

{imm[7], imm[7], imm[7], imm[7], imm[7], imm[7], imm[7], imm[7]}

```

と同じだが、よりすっきりした書き方である。この 8bit 分を元の imm とくっつけて 16bit にするので、これはすなわち符号拡張である。一方、ADDIU, LDIU は符号拡張 せず、8bit の 0 をくっつければ良いので、以下のように書けば良い。

#### {8'b0,imm}

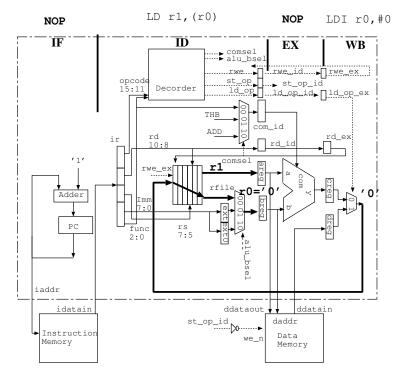

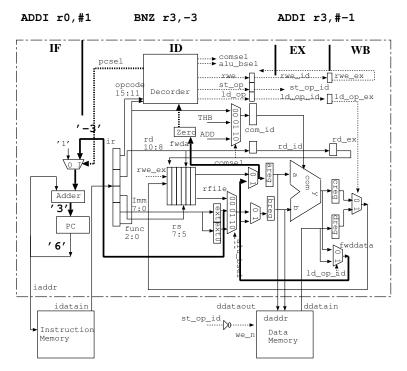

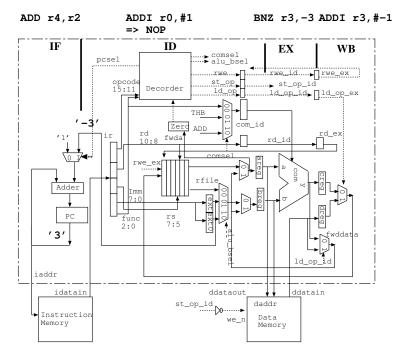

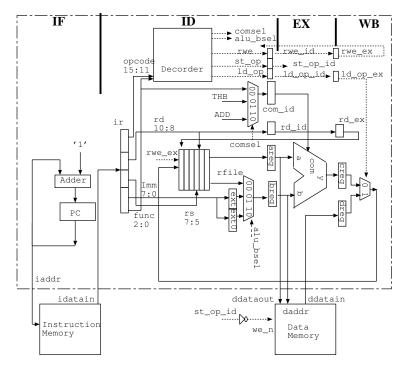

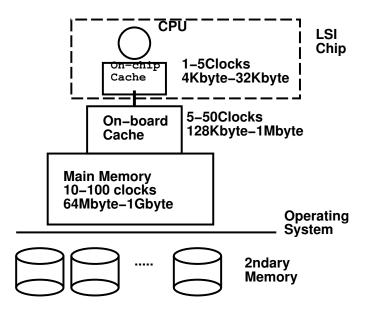

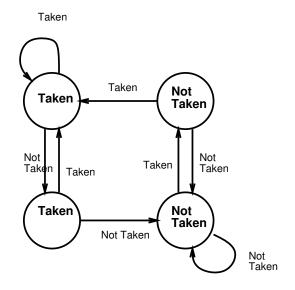

これ以外は、レジスタ同士の演算ということになるので、レジスタファイルから読み出したrfbをALUのB入力に入れてやる。